Cryptographic LSI

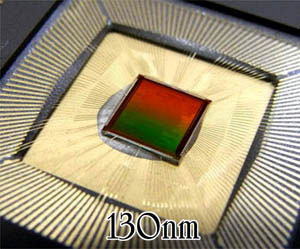

TSMC 130nm Version

This cryptographic LSI was fabricated with a 130-nm TSMC standard cell library. ISO/IEC 18033-3 standard block ciphers AES, Camellia, SEED, MISTY-1, CAST-128, a defact standard DES, and a public-key cipher RSA are supported. The key size for export version is limited as 56 bits for block ciphers and 512 bits for RSA.

- Cryptographic LSI for SASEBO-R Specification Ver. 1.0 (English)(pdf 371KB)

- Cryptographic LSI for SASEBO-R Specification Ver. 1.0 (Japanese)(pdf 418KB)

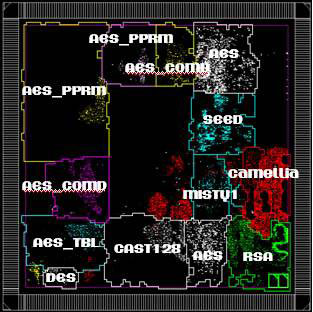

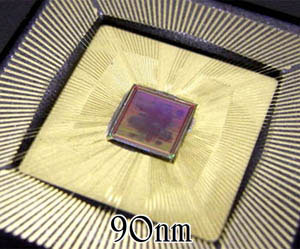

TSMC 65nm / 130nm Version - with Side-channel Attack Countermeasures

Two cryptographic LSIs fabricated with 90-nm and 130-nm TSMC standard cell libraries support elliptic curve cryptography as well as the ISO/IEC 18033-3 standard block ciphers and RSA. Seven AES circuits with side channel attack countermeasures are also integrated on the LISs.

- Standard Cryptographic LSI Specification -with Side Channel Attack Countermeasures- Ver. 1.0(pdf 6.95MB)

- Standard Cryptographic LSI Specification -with Side Channel Attack Countermeasures- Ver. 1.0 (Japanese)(pdf 7.02MB)

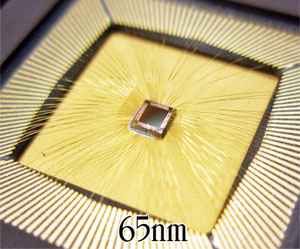

e-Shuttle 65nm Version - with Side-channel Attack Countermeasures

This LSI is fabricated with a 65-nm e-Shuttle standard cell library. This LSI supports CLEFIA developed by SONY Corporation as well as ISO/IEC 18033-3 standard block ciphers, RSA and ECC. Seven AES circuits with side-channel attack countermeasures are also integrated on the LSI.

Cryptographic IP Cores

In order to collect useful experimental data and results and subsequently establish standard evaluation metrics, standard hardware design of cryptographic algorithms is required, which can be implemented on the SASEBO boards. In this regard, RCIS and Tohoku University designed cryptographic hardware IP cores of all ISO/IEC 18033-3 standard block ciphers (AES, Camellia, SEED, MISTY-1, CAST-128), DES, and the public key cipher RSA. The cryptographic ASIC chip used in SASEBO-R contains all relevant cryptographic IP macros.

The IP cores, designed in Verilog-HDL, were released online free of charge at the following links. Reading the usage conditions and restrictions is strongly recommended.