暗号LSI

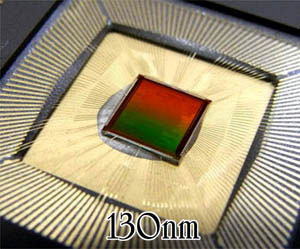

TSMC 130nm 版

TSMC社の130nmスタンダードセルライブラリを用いて製造された暗号LSIは,ISO/IEC 18033-3標準のブロック暗号であるAES,Camellia,SEED,MISTY-1,CAST-128,デファクトスタンダードのDES,そして公開鍵暗号のRSAをサポートし,AES暗号はDPA対策を施した回路です.海外向けバージョンでは,ブロック暗号の鍵長は56ビットに,RSA暗号は512ビットに制限されています.

- サイドチャネル攻撃評価用ISO/IEC 標準暗号LSI仕様書 第1版(pdf 418KB)

- Cryptographic LSI for SASEBO-R specification Ver. 1.0 (pdf 371KB)

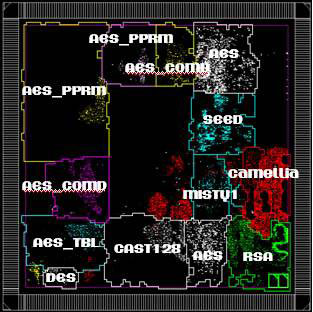

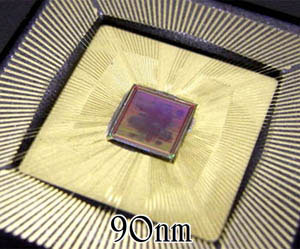

TSMC 90nm / 130nm サイドチャネル攻撃対策版

TSMC社の90nmおよび130nmスタンダードセルライブラリを用いて製造された暗号LSIは,ISO/IEC18033-3標準のブロック暗号とRSA暗号に加えて,楕円曲線暗号をサポートしています.また,サイドチャネル攻撃対を施した7種類を含む13種類のAES回路も実装しています.

- 標準暗号LSI仕様書 ∼サイドチャネル攻撃対策版∼ 第1版 (pdf 7.02MB)

- Standard Cryptographic LSI Specification -with Side Channel Attack Countermeasures- Ver. 1.0(pdf 6.95MB)

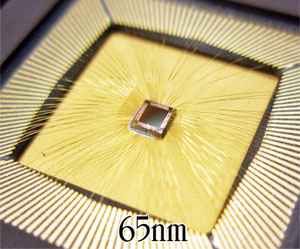

e-Shuttle 65nm サイドチャネル攻撃対策版

e-Shuttle の 65nm スタンダードセルライブラリを用いて製造された暗号LSIは,ISO/IEC 18033-3標準のブロック暗号,RSA暗号,楕円曲線暗号に加え,SONYによって開発されたCLEFIA暗号が搭載されています.また,サイドチャネル攻撃対策やフォルト攻撃対策を実装した7種類を含む13種類のAESを搭載しています.

暗号IPコア

新たな評価指針の策定に向けて有用な実験データと結果を収集するためには,SASEBO上に実装可能な,各種暗号アルゴリズムの標準的な回路デザインが必要となります.そこで,情報セキュリティ研究センターと東北大学は全てのISO/IEC 18033-3標準ブロック暗号(AES, Camellia, SEED, MISTY-1, CAST-128)とDES,そして公開鍵暗号RSAの回路IPコアを開発しました.上述のSASEBO-R用の暗号LSIには,これら全てのIPコアが実装されています.

このIPコアのVerilog-HDLソースコードは,学術研究目的に下記のリンクから無料でダウンロードすることができます.使用に際しては「使用条件および制限」を必ず参照してください.