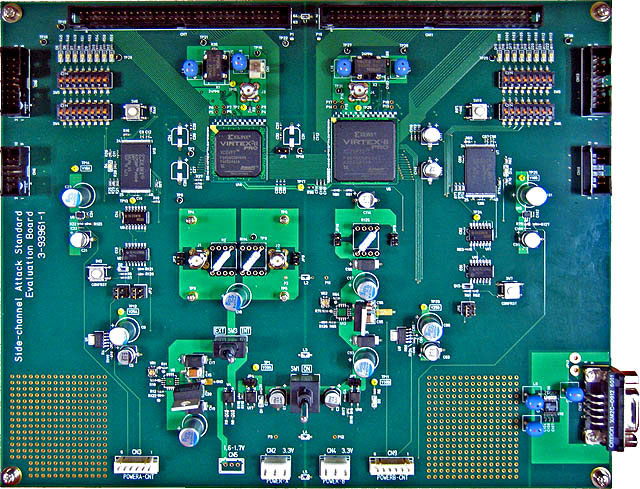

SASEBO

The original SASEBO FPGA board with Xilinx® Virtex™-II Pro devices xc2vp7 and xc2vp30.

- SASEBO specification Ver. 1.0 (English)(pdf 1.65MB)

- SASEBO specification Ver. 1.0 (Japanese)(pdf 1.72MB)

- Electrical characterization test for 80 SASEBO boards(pdf 51KB)

- SASEBO-AES specification Ver. 1.3 for JCMVP (Japanese)(pdf 1.71MB)