|

|

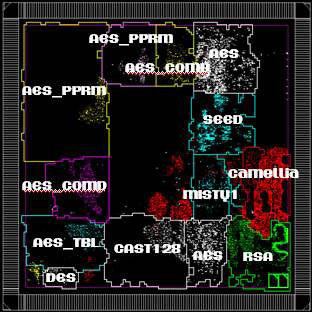

In order to collect useful experimental data and results and subsequently

establish standard evaluation metrics, standard hardware design of cryptographic

algorithms is required, which can be implemented on the SASEBO boards.

In this regard, cryptographic hardware IP cores of all ISO/IEC 18033-3

standard block ciphers (AES, Camellia, SEED, MISTY-1, CAST-128), DES, and

the public key cipher RSA were designed. The cryptographic ASIC chip used

in SASEBO-R contains all relevant cryptographic IP macros.

The IP cores, designed in Verilog-HDL, were released online free of charge

at the following links. Reading the usage conditions and restrictions is strongly

recommended.

|