# Side-channel AttacK User Reference Architecture SAKURA-W Quick Start Guide

[Version 0.9]

October 19, 2014

Satoh Laboratory,

The University of Electro Communications

### **Revision Record**

| Date       | Version | Record   |

|------------|---------|----------|

| 2014/10/19 | 0.9     | Released |

|            |         |          |

# **Contents**

| 1. | Ove | erview                            | . 2 |

|----|-----|-----------------------------------|-----|

| 2. | Hai | rdware Device                     | . 2 |

| 3. | Do  | wnload and install software on PC | . 2 |

| 4. | SA  | KURA-G Setup                      | .3  |

|    | 4.1 | DIP Switch                        | .3  |

|    | 4.2 | Download SAKURA-W Tool Package    | . 4 |

| 5. | SA  | KURA-G Configuration              | . 4 |

|    | 5.1 | FPGA Configuration                | . 4 |

|    | 5.2 | USB Controller Configuration.     | . 5 |

| 6. | SA  | KURA-W Setup                      | . 7 |

| 7. | Ope | eration                           | . 7 |

| ,  | 7.1 | Power on SAKURA-G                 | . 7 |

| ,  | 7 2 | Execute SAKURA-W Checker          | 8   |

### 1. Overview

This document briefly describes instruction to conduct side channel attack experiments using an IC on SAKURA-W board. Required hardware devices, device drivers and basic tools, board configuration, and boar operation are described below.

### 2. Hardware Device

The following equipment are required to operate the SAKURA-W board.

#### SAKURA-W bard

An IC card R/W board to be stacked on SAKURA-G

### 2. SAKURA-G bard

This board is used as a mother board for SAKURA-W.

### 3. IC card

ATMega8515 card delivered with SAKURA-W, which contains DES and AES binary codes.

### 4. USB cable

A standard USB B-A type cable to connect the SAKURA-G board and a personal computer. 5-V power is supplied from the computer to SAKURA-G through this cable.

### 5. Personal computer

Windows Vista/7 middle-range personal computer to control SAKURA-G.

### 6. FPGA configuration cable

The cable is used to configure control and cryptographic FGAs on SAKURA-G. Xilinx platform cable USB II is highly recommended.

### 3. Download and install software on PC

Some Windows drives and tools are required to download from the following URLs to configure and to control SAKURA-G and W. Please follow instructions of each software to for installation and operation.

### 1. Microsoft.Net Framework 4.0

<Japanese version>

http://www.microsoft.com/downloads/details.aspx?FamilyID=333325fd-ae52-4e35-b531-508d977d32a6&displaylang=ja

<US version>

http://www.microsoft.com/downloads/details.aspx?FamilyID=333325fd-ae52-4e35-b531-508 d977d32a6

### 2. Xilinx ISE 14.6

<Japanese version>

http://japan.xilinx.com/ise\_eval/index.htm

<US Version>

http://www.xilinx.com/ise\_eval/index.htm

### 3. Two FTDI drivers

<D2XX driver>

http://www.ftdichip.com/Drivers/D2XX.htm

<FTD2XX\_NET\_DLL>

http://www.ftdichip.com/Projects/CodeExamples/CSharp.htm FTD2XX\_NET\_DLL should be copied into the same directory where SAKURA\_Checker.exe is copied.

### 4. FT\_prog

http://www.ftdichip.com/Support/Utilities.htm

FT\_prog.exe is a stand-alone tool, and thus no installation process is required.

# 4. SAKURA-G Setup

### 4.1 DIP Switch

SAKRA-W is controlled by Xilinx Spaltan-6 FPGA on SAKURA-G, and thus SAKURA-G must be setup as follows.

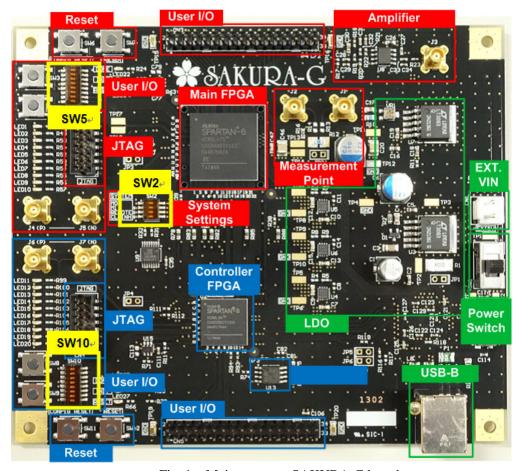

Fig. 1 shows major parts on the SAKURA-G board and locations of DIP switches and setup for the switch SW2 is shown in Tables 1. SW5 and SW10 are not used for SAKURA-W control.

Fig. 1 Major parts on SAKURA-G board.

Table 1. SW2 set up

| Pin | Setup | Remarks |

|-----|-------|---------|

| 1   | ON    | MO      |

| 2   | OFF   | M1      |

| 3   | OFF   | REMOTE  |

| 4   | OFF   | CLKINH  |

### 4.2 Download SAKURA-W Tool Package

Access to the following SAKURA-W Webpage.

http://satoh.cs.uec.ac.jp/SAKURA/hardware/SAKURA-W.html

Then, download following four files, and unzip them into the PC connected to SAKURA-G and -W.

SAKURA-G interface circuits in VCP mode for SAKURA-W control

This file contains Verilog-HDL codes, a ucf file, and ROM files (bit and mcs) for the controller FPGA XC6SLX9 on SAKURA-G.

### 2. SAKURA-W DES Checker

This file contains a Windows program to test a DES function of the ATMega8515 card in "Release" folder.

- 3. SAKURA-W AES Checker

- 4. This file contains a Windows program to test a AES function of the ATMega8515 card in "Release" folder.

- SAKURA-W Quick Start Guide This document.

# 5. SAKURA-G Configuration

## **5.1** FPGA Configuration

After confirming the power switch SW1 is set to OFF (center position), connect SAKURA-G (connecter CN6) to PC by using USB cable as shown in Fig. 2. In order to configure SPI ROM for the controller FPGA XC6SLX9, connect a configuration cable to the JTAG connector CN4 as shown in Fig. 3. The board should be kept power-off during the cable connection.

Fig. 2 SAKURA-G connected to PC by a USB cable.

Fig. 3 Configuration cable attached to a JTAG connector of the control FPGA.

In order to configure the FPGA, turn on the power witch SW1 (set to the USB side), and execute iMACT software on PC. In the iMPAC, select a configuration file "sakura\_w\_vcp\_mode.mcs" in the unzipped directory. Then select SPI PROM / AT45DB321D as shown in Fig. 4, and write the mcs file into PROM.

Fig. 4 ROM selection.

### 5.2 USB Controller Configuration

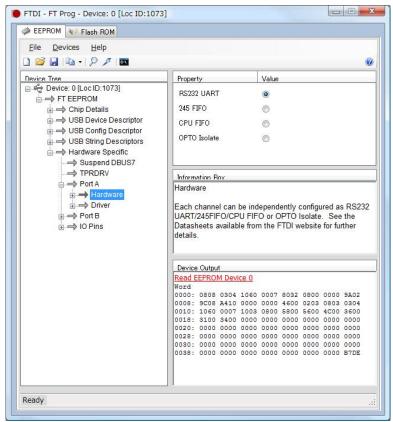

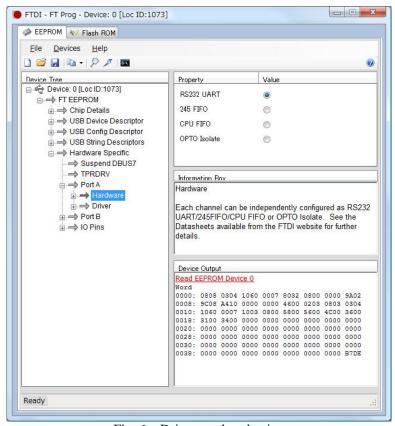

In order to enable the USB interface of SAKURA-G, a USB controller chip should be configured using FT\_Prog.exe downloaded from FTDI's Website in chapter 3. First, select hardware operation mode "RS232 UART" from four modes as shown in Fig. 5. Then, select driver mode "Virtual COM Port" as shown in Fig. 6. The selection is applied only to port A. After that, write the setting into EEPROM of the USB controller chip. More details please refer FTDI's user's manual.

Fig. 5 Operation mode selection

Fig. 6 Driver mode selection

# 6. SAKURA-W Setup

Turn off the power switch and disconnect the USB cable for SAKURA-G, and mount SKURA-W on SAKURA-W as shown in Fig. 7. There are five jumper headers JP1-JP5, but JP1 and JP2 are not used in this VCP mode. JP3-JP5 are used to set a power supply voltage to the IC card as follows.

JP3: 1.8V JP4: 3.0V

JP5: 1.0-3.8V (Adjustable)

For the ATMega8515 card, set a jumper plug to JP4.

Fig. 7 SAKURA-W on SAKURA-G

# 7. Operation

### 7.1 Power on SAKURA-G

When the SAKURA-W is setup properly, connect a USB cable to SAKURA-G and turn on the power switch. Then LED10-LED20 of SAKURA-G and LED1-5 of SAKURA-W are as shown in Tables 4 and 5, respectively. If the status is different, data may not be written in the ROMs for FPGA and USB properly.

Table 4 Status LED of SAKURA-G

| No.   | Status | No.   | Status |

|-------|--------|-------|--------|

| LED11 | off    | LED16 | off    |

| LED12 | off    | LED17 | off    |

| LED13 | off    | LED18 | off    |

| LED14 | on     | LED19 | off    |

| LED15 | off    | LED20 | off    |

Table 5 Status LED of SAKURA-W

| No.   | Status |  |

|-------|--------|--|

| LED16 | off    |  |

| LED17 | off    |  |

| LED18 | off    |  |

| LED19 | off    |  |

| LED20 | off    |  |

### 7.2 Execute SAKURA-W Checker

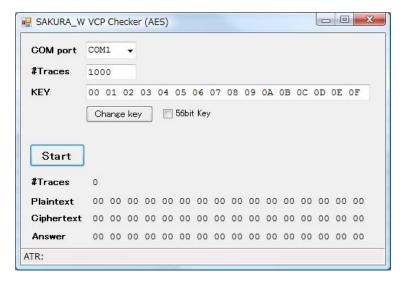

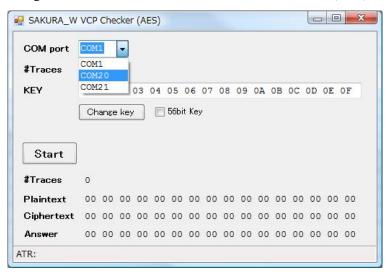

Execute the AES function check program for the ATMega8515 card "SAKURA\_W\_VCP\_Checker/bin/Release/SAKURA\_W\_VCP\_Checker.exe" downloaded and unzipped as described in Chapter 3. Fig. 7 shows the initial window of the checker. Followings are explanation of each part in the window. The checker to test DES operations of the card is almost the same except the key length.

### COM port

Selection of COM port connected to SAKURA-G as shown in Fig. 8.

### #Traces

Input a number of encrypt operations to be performed.

### Key

A 128-bit secret key used for the encryption.

### Change Key

The 128-bit secret key is changed randomly by clicking this button.

### 56-bit Key

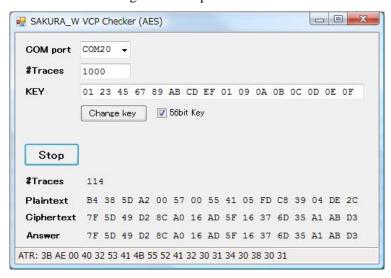

A length of the secret key for the ATMega8515 card delivered with SAKURA-W is limited to 56 bit (72 bits from MSB side are fixed to "01 23 45 67 89 AB CD EF 01") due to an export regulation. Therefore, it is required to check this box to execute the AES function as shown in Fig. 8. A user can re-program the card with a 128-bit key AES code on the SAKURA-W page.

### Start/Stop

When Start button is clicked, encrypt operation starts and the button changes to "Stop" button window changed as shown in Fig. 9. When the Stop button is clicked, encrypt operation is stopped. Even if this button is not clicked, encrypt operation is stopped when encryption is repeated the number of times indicated by "Traces" or error occurs.

### #Traces

A number of encrypt operations performed.

### **Plaintext**

A 128-bit plaintext being encrypted. The plaintexts are generated randomly.

### Cipher text

A 128-bit cipher text encrypted from the plaintext.

### Answer

A 128-bit cipher text returned from the IC card through SAKURA-W and -G.

Fig. 7 Initial window of SAKURA\_W\_VCP\_Cheker (AES)

Fig. 8 COM port selection

Fig. 9 Encrypt operation with 56-bit key

When the encrypt operation is repeated the number indicated by #Trace and no error occurred, the message dialog box shown in Fig. 10 appears. Thus click "ok" button.

Fig. 10 Successful completion

### ${\hbox{$\mathbb C$}} \ {\bf Satoh} \ {\bf Laboratory}$

Department of Communication Engineering and Informatics The University of Electro-Communications 1-5-1 Chofugaka, Chofu, Tokyo, 182-8585, Japan

sakura@mtmsystems.jp http://satoh.cs.uec.ac.jp/SAKURA/