**標準暗号 LSI 仕様書**

**～サイドチャネル攻撃対策版～**

**Standard Cryptographic LSI Specification**

**～with Side Channel Attack Counter Measures～**

[第 1.0 版]

**2009 年 8 月 1 日**

(独) 産業技術総合研究所

情報セキュリティ研究センター

# 目次

|                                       | Page |

|---------------------------------------|------|

| 1. 概要                                 | 1    |

| 2. 外部仕様                               | 3    |

| 2.1 入出力信号                             | 3    |

| 2.2 コマンド制御                            | 13   |

| 3. 内部詳細仕様                             | 18   |

| 3.1 LSI 内部構成                          | 18   |

| 3.2 外部インターフェース                        | 21   |

| 3.3 インタフェースレジスタ                       | 22   |

| 3.4 クロックツリー                           | 29   |

| 3.5 リセット                              | 30   |

| 3.6 付帯機能                              | 30   |

| 4. LSI の物理レイアウト                       | 35   |

| 4.1 130nm バージョン                       | 35   |

| 4.2 90nm バージョン                        | 45   |

| 5. 暗号ハードウェア IP コア                     | 53   |

| 5.1 AES0 (合成体 S-box)                  | 53   |

| 5.2 AES1/AES2/AES3/AES4 (各種 S-box 実装) | 56   |

| 5.3 AES5 (CTR モード)                    | 58   |

| 5.4 AES6 (FA 対策版)                     | 64   |

| 5.5 AES7 (ラウンド鍵事前生成)                  | 68   |

| 5.6 AES8 (MAO)                        | 70   |

| 5.7 AES9 (MDPL)                       | 71   |

| 5.8 AES10 (Threshold Implementation)  | 72   |

| 5.9 AES11 (WDDL)                      | 72   |

| 5.10 AES12/AES13 (疑似 RSL)             | 73   |

| 5.11 Camellia                         | 73   |

| 5.12 CAST-128                         | 76   |

| 5.13 DES                              | 79   |

| 5.14 ECC                              | 82   |

| 5.15 MISTY1                           | 85   |

| 5.16 RSA                              | 88   |

| 5.17 SEED                             | 92   |

| 5.18 TDES                             | 95   |

| 文献                                    | 98   |

# 1. 概要

「標準暗号アルゴリズムを実装した専用 LSI」(以下、暗号 LSI)は、差分電力解析を始めとする各種実装攻撃の評価を目的に、公開鍵暗号 RSA、楕円曲線暗号(ECC)、および ISO/IEC 18033 (Information technology- Security techniques - Encryption algorithms) Part3:Block ciphers に掲載された全ての共通鍵暗号アルゴリズムを実装したものである。暗号 LSI は TSMC(Taiwan Semiconductor Manufacturing Company)社の 130nm および 90nm の CMOS プロセスを用いて製造され、160 ピン QFP セラミックパッケージで封止されている。

実装したアルゴリズムは下記の 9 種で、AES については異なる 14 種類の実装を行っているため、計 22 種類の暗号コアの搭載となった。なお、AES の実装⑧～⑬は論理合成をカスタムで行っている。国内だけでなく海外でも評価実験に使用するため、輸出規制を受けないよう鍵長に制限を与えている。DES 以外のブロック暗号の秘密鍵 128bit の上位 72bit を固定し、56bit のみユーザが指定できるようにしており、RSA 暗号は 512bit 鍵だけをサポートしている。AES0～AES7/Camellia /CAST/DES/SEED/MISTY1/RSA/T-DES は東北大学大学院情報科学科青木研究室と産業技術総合研究所情報セキュリティ研究センターが、AES8～AES11 は横浜国立大学大学院 環境情報研究院松本研究室が、AES12～AES13 は三菱電機株式会社情報技術総合研究所が、ECC は電気通信大学情報通信工学科太田・崎山研究室がそれぞれ独自に開発したものである。本事業において学術的研究を促進する目的で無償にて提供を受けているが、これらの暗号回路マクロの著作権は各機関に帰属する。5 章ではこれら暗号マクロ個々の仕様について解説を行うが、そこに敬意際した仕様書は、各機関が作成したものに各機関の許可を得て和訳、加筆・修正を行っている。したがって、それら仕様書の著作権も暗号マクロ毎に、それを作成した研究機関に所属する。なお、東北大学提供の暗号回路のソースコードおよび英文仕様書は、“Cryptographic Hardware Project” (<http://www.aoki.ecei.tohoku.ac.jp/crypto/>) からダウンロードすることができる。また 5 章において、サイドチャネル対策を施した AES8～13 の解説は、その対策アルゴリズムの概要を述べるにとどめ、マクロの詳細なデータパスアーキテクチャについては非公開とする。

- AES(鍵長:128bit)

- ①S-Box 実装→合成体、暗号化/復号サポート

- ②S-Box 実装→case 文記述、暗号化のみサポート

- ③S-Box 実装→AND-XOR 実装(1-Stage)、暗号化のみサポート

- ④S-Box 実装→AND-XOR 実装(3-Stage)、暗号化のみサポート

- ⑤CTR モードサポートバイオペレーティングシステム実装

- ⑥故障攻撃耐性評価用実装

- ⑦ラウンド鍵を事前計算する実装

- ⑧DPA 対策評価用実装(Masked AND Operation)

- ⑨DPA 対策評価用実装(MDPL)

- ⑩DPA 対策評価用実装(Threshold Implementation)

- ⑪DPA 対策評価用実装(WDDL)

- ⑫DPA 対策評価用実装(擬似 RSL)

- ⑬DPA 対策評価用実装(擬似 RSL の効果評価用)

- Camellia(鍵長:128) 暗号化/復号サポート

- SEED:暗号化/復号サポート

- MISTY1:暗号化/復号サポート

- Triple-DES:3Key, 暗号化/復号サポート

- DES:暗号化/復号サポート

- CAST128:暗号化/復号サポート

- ECC: 鍵長は 64bit. 標数 2 の体における点のスカラ一倍算

- RSA: 512bit のべき乗剩余演算

主な機能は、下記のとおりである。

- 暗号アルゴリズムの実行

- 平成 19 年度に開発された暗号 LSI 専用のサイドチャネル攻撃用標準評価ボード SASEBO-R (Side-channel Attack Standard Evaluation Board) 上に実装し、ボード上の FPGA Virtex-II PRO xc2vp30 とインターフェースする機能

- 電力情報等サンプリング用のトリガ信号出力機能。 (トリガ信号出力の抑止も可能)

- 故障攻撃時の評価を目的として、事前に設定したアルゴリズム処理の中間値、中間鍵の出力機能(上記⑥の AES コアのみサポート)

- 故障攻撃時の評価を目的として、故障発生時の中間値と中間鍵の出力機能(上記⑥の AES コアのみサポート)

- 0.3 秒毎に自動的に暗号処理を継続する自走モードのサポート(上記⑥の AES コアのみサポート)

## 2. 外部仕様

### 2.1 入出力信号

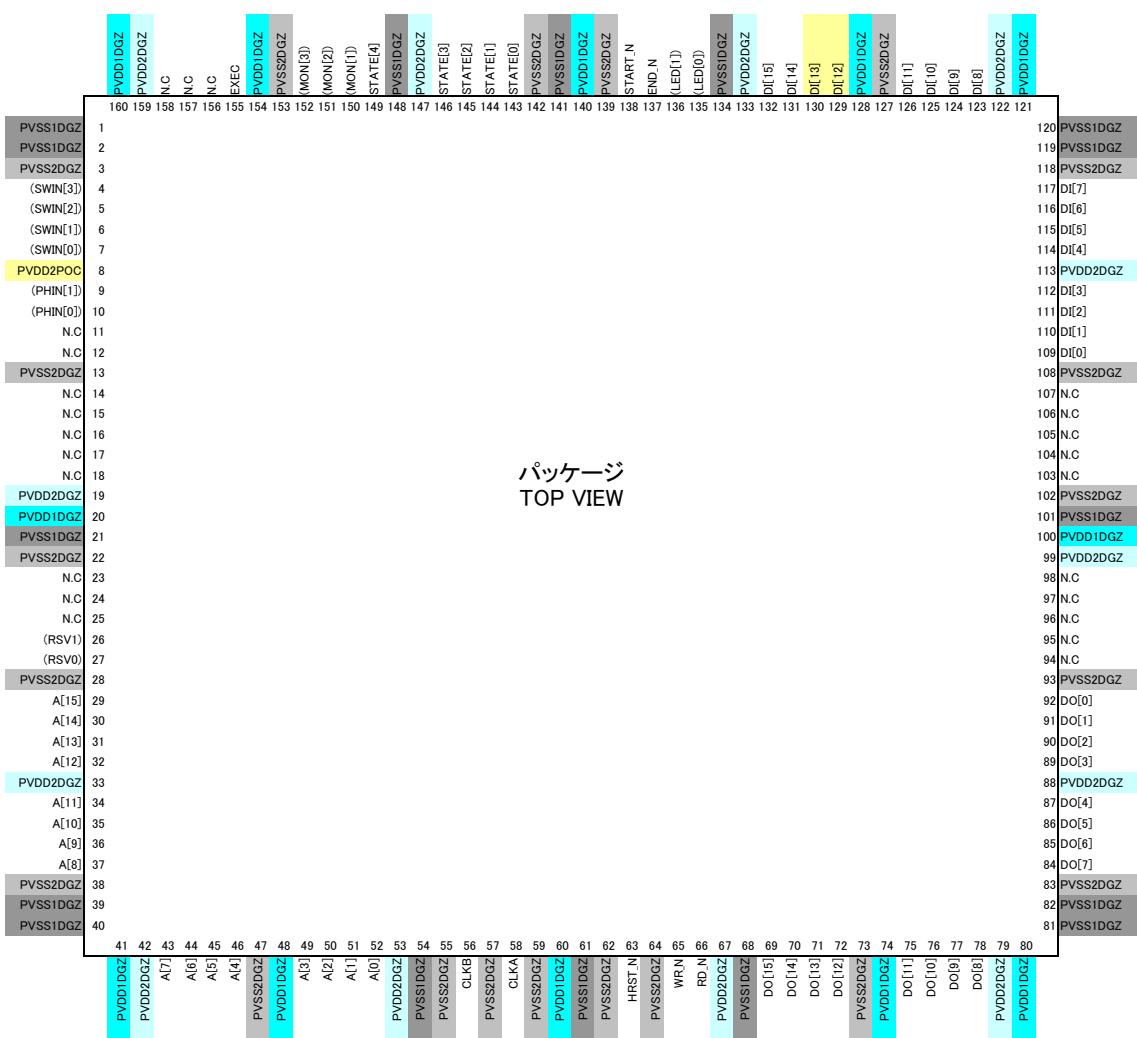

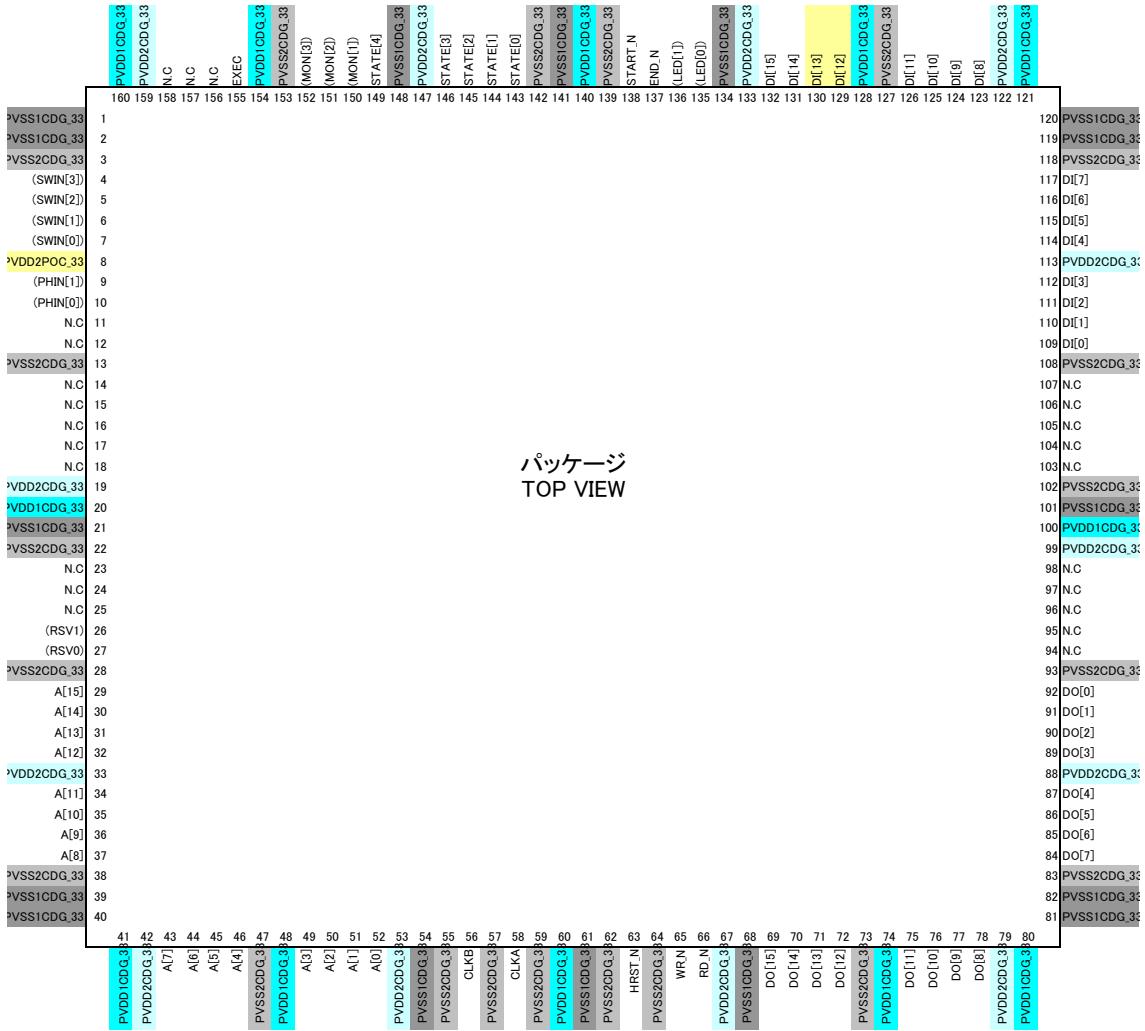

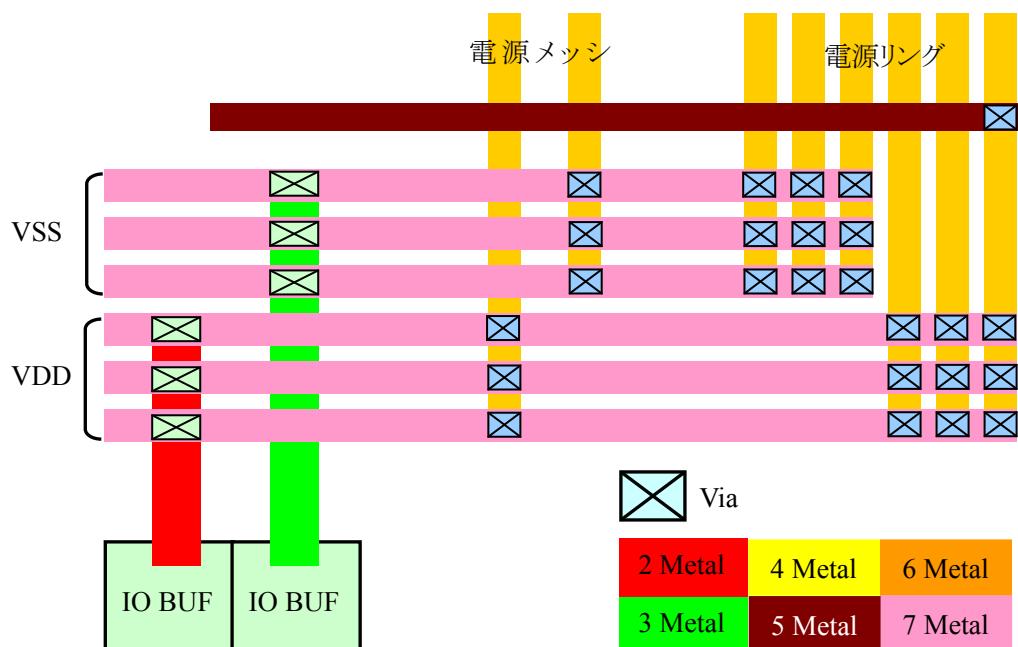

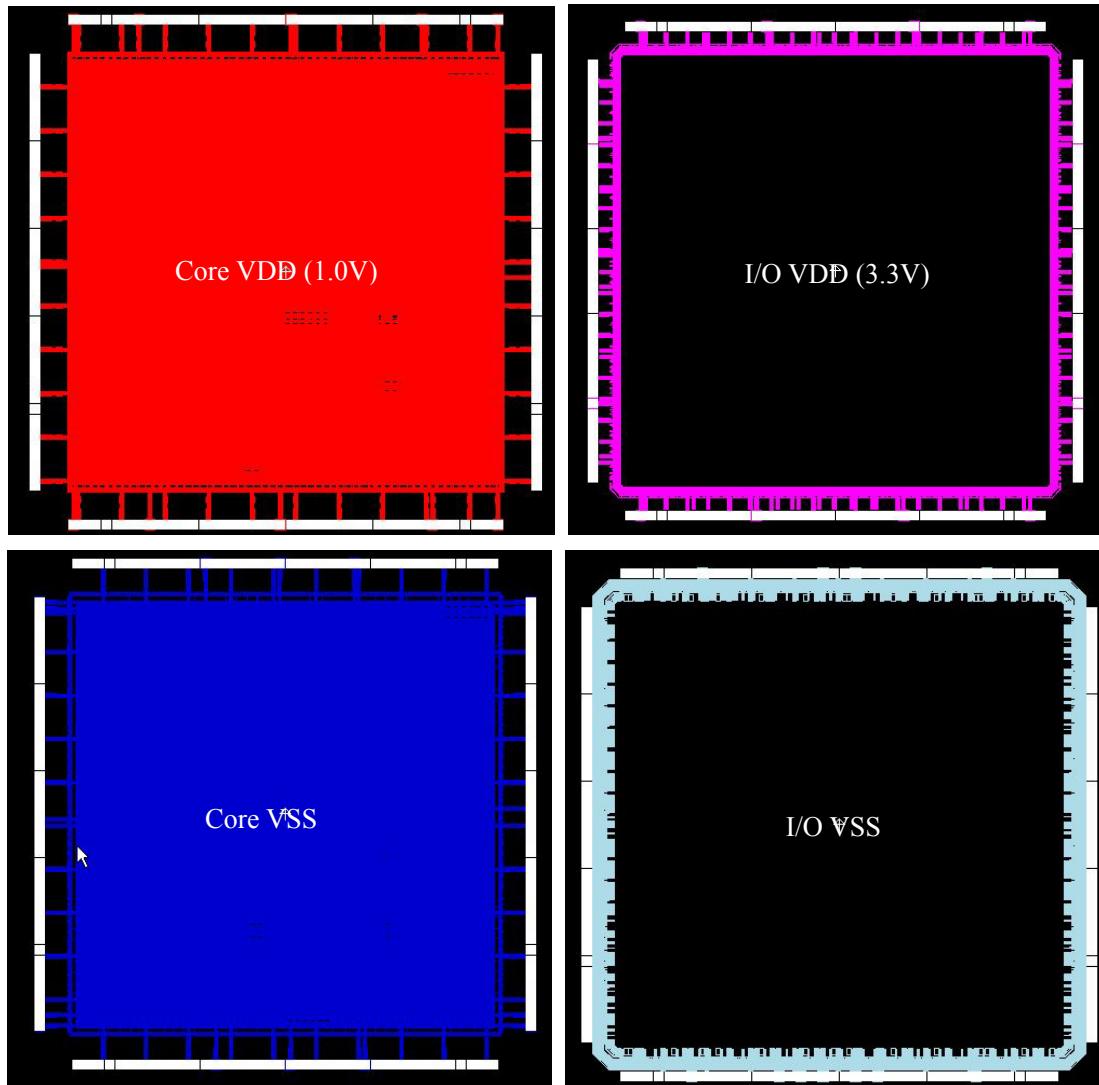

表 2.1 に暗号 LSI の入出力信号の概要を、表 2.2 および図 2.1 に 130nm 版の 160 ピンのアサインを、表 2.3 および図 2.2 に 90nm 版のピンアサインを示す。130nm 版と 90nm 版では、コア電源が異なる以外( $1.2V \pm 0.12$  および  $1.0V \pm 0.1V$ )は、パッケージ寸法、ピン配置、および論理的インターフェースは同一である。表 2.2 の「Signal Name」中の()は将来の拡張用であることを意味し、暗号 LSI では未使用であり。また、VSS/VDD ピンは「Signal Name」にセル名を記載している。暗号 LSI では、ノイズを減らし暗号アルゴリズム処理の電力や電磁波を精度よく測定するため、LSI 内部と入出力バッファの VDD/VSS を分離する構成とした。

表 2.1 入出力信号

| 分類<br>(総数)     | 信号名        | 本数 | 有意 | 方向<br>(LSI 側から) | 用途・備考                                                     |

|----------------|------------|----|----|-----------------|-----------------------------------------------------------|

| システム<br>(11)   | CLKA       | 1  | -- | IN              | 24MHz の LSI 内部回路用クロック入力。CLKB と全く同一、もしくはより周波数の高いクロックを入力のこと |

|                | CLKB       | 1  | -- | IN              | LSI インタフェース回路用クロック                                        |

|                | HRST_N     | 1  | L  | IN              | ボード上のリセット回路によって生成されるリセット信号。非同期リセット入力                      |

|                | LEDO[1:0]  | 2  | L  | OUT             | LED 駆動用出力(NC ピン)                                          |

|                | SWIN[3:0]  | 4  | -- | IN              | スイッチ用入力(NC ピン)                                            |

|                | PHIN[1:0]  | 2  | -- | IN              | ピンヘッダ用入力(NC ピン)                                           |

| バス制御<br>(4)    | WR_N       | 1  | L  | IN              | 書き込み指示                                                    |

|                | RD_N       | 1  | L  | IN              | 読み出し指示                                                    |

|                | RSV0       | 1  | -- | IN              | (NC ピン)                                                   |

|                | RSV1       | 1  | -- | IN              | (NC ピン)                                                   |

| バスアドレス<br>(16) | A[15:0]    | 16 | -- | IN              |                                                           |

| バスデータ<br>(32)  | DI[15:0]   | 16 | -- | IN              | 入力データ                                                     |

|                | DO[15:0]   | 16 | -- | OUT             | 出力データ                                                     |

| 評価用<br>(13)    | START_N    | 1  | L  | OUT             | ターゲット処理開始                                                 |

|                | END_N      | 1  | L  | OUT             | ターゲット処理完了                                                 |

|                | (TRIG0)    | 1  | -- | OUT             | (NC ピン)                                                   |

|                | (TRIG1)    | 1  | -- | OUT             | (NC ピン)                                                   |

|                | EXEC       | 1  | H  | OUT             | ターゲット処理中                                                  |

|                | STATE[3:0] | 4  | -- | OUT             | 選択 IP を示す                                                 |

|                | MON[3:0]   | 4  | -- | OUT             | 内部モニタ用(詳細未定)                                              |

| 計              |            | 77 |    |                 |                                                           |

表 2.2 130nm 版 LSI ピンアサイン (1/4)

| Pin NO | Signal Name | I/O | I/F Voltage | output | I/O Buffer | Function  |

|--------|-------------|-----|-------------|--------|------------|-----------|

| 1      | PVSS1DGZ    |     |             |        |            | core GND  |

| 2      | PVSS1DGZ    |     |             |        |            | core GND  |

| 3      | PVSS2DGZ    |     |             |        |            | I/O GND   |

| 4      | (SWIN[3])   |     |             |        |            | N.C       |

| 5      | (SWIN[2])   |     |             |        |            | N.C       |

| 6      | (SWIN[1])   |     |             |        |            | N.C       |

| 7      | (SWIN[0])   |     |             |        |            | N.C       |

| 8      | PVDD2POC    |     |             |        |            | I/O 3.3V  |

| 9      | (PHIN[1])   |     |             |        |            | N.C       |

| 10     | (PHIN[0])   |     |             |        |            | N.C       |

| 11     | N.C         |     |             |        |            | N.C       |

| 12     | N.C         |     |             |        |            | N.C       |

| 13     | PVSS2DGZ    |     |             |        |            | I/O GND   |

| 14     | N.C         |     |             |        |            | N.C       |

| 15     | N.C         |     |             |        |            | N.C       |

| 16     | N.C         |     |             |        |            | N.C       |

| 17     | N.C         |     |             |        |            | N.C       |

| 18     | N.C         |     |             |        |            | N.C       |

| 19     | PVDD2DGZ    |     |             |        |            | I/O 3.3V  |

| 20     | PVDD1DGZ    |     |             |        |            | core 1.2V |

| 21     | PVSS1DGZ    |     |             |        |            | core GND  |

| 22     | PVSS2DGZ    |     |             |        |            | I/O GND   |

| 23     | N.C         |     |             |        |            | N.C       |

| 24     | N.C         |     |             |        |            | N.C       |

| 25     | N.C         |     |             |        |            | N.C       |

| 26     | (RSV1)      |     |             |        |            | N.C       |

| 27     | (RSV0)      |     |             |        |            | N.C       |

| 28     | PVSS2DGZ    |     |             |        |            | I/O GND   |

| 29     | A[15]       | I   | 3.3V        |        | PDIDGZ     | アドレスバス    |

| 30     | A[14]       | I   | 3.3V        |        | PDIDGZ     | アドレスバス    |

| 31     | A[13]       | I   | 3.3V        |        | PDIDGZ     | アドレスバス    |

| 32     | A[12]       | I   | 3.3V        |        | PDIDGZ     | アドレスバス    |

| 33     | PVDD2DGZ    |     |             |        |            | I/O 3.3V  |

| 34     | A[11]       | I   | 3.3V        |        | PDIDGZ     | アドレスバス    |

| 35     | A[10]       | I   | 3.3V        |        | PDIDGZ     | アドレスバス    |

| 36     | A[9]        | I   | 3.3V        |        | PDIDGZ     | アドレスバス    |

| 37     | A[8]        | I   | 3.3V        |        | PDIDGZ     | アドレスバス    |

| 38     | PVSS2DGZ    |     |             |        |            | I/O GND   |

| 39     | PVSS1DGZ    |     |             |        |            | core GND  |

| 40     | PVSS1DGZ    |     |             |        |            | core GND  |

表 2.2 130nm 版 LSI ピンアサイン (2/4)

| Pin NO | Signal Name | I/O | I/F Volatage | output | I/O Buffer | Function   |

|--------|-------------|-----|--------------|--------|------------|------------|

| 41     | PVDD1DGZ    |     |              |        |            | core 1.2V  |

| 42     | PVDD2DGZ    |     |              |        |            | I/O 3.3V   |

| 43     | A[7]        | I   | 3.3V         |        | PDIDGZ     | アドレスバス     |

| 44     | A[6]        | I   | 3.3V         |        | PDIDGZ     | アドレスバス     |

| 45     | A[5]        | I   | 3.3V         |        | PDIDGZ     | アドレスバス     |

| 46     | A[4]        | I   | 3.3V         |        | PDIDGZ     | アドレスバス     |

| 47     | PVSS2DGZ    |     |              |        |            | I/O GND    |

| 48     | PVDD1DGZ    |     |              |        |            | core 1.2V  |

| 49     | A[3]        | I   | 3.3V         |        | PDIDGZ     | アドレスバス     |

| 50     | A[2]        | I   | 3.3V         |        | PDIDGZ     | アドレスバス     |

| 51     | A[1]        | I   | 3.3V         |        | PDIDGZ     | アドレスバス     |

| 52     | A[0]        | I   | 3.3V         |        | PDIDGZ     | アドレスバス     |

| 53     | PVDD2DGZ    |     |              |        |            | I/O 3.3V   |

| 54     | PVSS1DGZ    |     |              |        |            | core GND   |

| 55     | PVSS2DGZ    |     |              |        |            | I/O GND    |

| 56     | CLKB        | I   | 3.3V         |        | PDISDGZ    | クロック.シミュット |

| 57     | PVSS2DGZ    |     |              |        |            | I/O GND    |

| 58     | CLKA        | I   | 3.3V         |        | PDISDGZ    | クロック.シミュット |

| 59     | PVSS2DGZ    |     |              |        |            | I/O GND    |

| 60     | PVDD1DGZ    |     |              |        |            | core 1.2V  |

| 61     | PVSS1DGZ    |     |              |        |            | core GND   |

| 62     | PVSS2DGZ    |     |              |        |            | I/O GND    |

| 63     | HRST_N      | I   | 3.3V         |        | PDISDGZ    | リセット.シミュット |

| 64     | PVSS2DGZ    |     |              |        |            | I/O GND    |

| 65     | WR_N        | I   | 3.3V         |        | PDIDGZ     | 書き込み指示     |

| 66     | RD_N        | I   | 3.3V         |        | PDIDGZ     | 読み出し指示     |

| 67     | PVDD2DGZ    |     |              |        |            | I/O 3.3V   |

| 68     | PVSS1DGZ    |     |              |        |            | core GND   |

| 69     | DO[15]      | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ      |

| 70     | DO[14]      | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ      |

| 71     | DO[13]      | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ      |

| 72     | DO[12]      | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ      |

| 73     | PVSS2DGZ    |     |              |        |            | I/O GND    |

| 74     | PVDD1DGZ    |     |              |        |            | core 1.2V  |

| 75     | DO[11]      | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ      |

| 76     | DO[10]      | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ      |

| 77     | DO[9]       | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ      |

| 78     | DO[8]       | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ      |

| 79     | PVDD2DGZ    |     |              |        |            | I/O 3.3V   |

| 80     | PVDD1DGZ    |     |              |        |            | core 1.2V  |

表 2.2 130nm 版 LSI ピンアサイン (3/4)

| Pin NO | Signal Name | I/O | I/F Volatage | output | I/O Buffer | Function  |

|--------|-------------|-----|--------------|--------|------------|-----------|

| 81     | PVSS1DGZ    |     |              |        |            | core GND  |

| 82     | PVSS1DGZ    |     |              |        |            | core GND  |

| 83     | PVSS2DGZ    |     |              |        |            | I/O GND   |

| 84     | DO[7]       | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ     |

| 85     | DO[6]       | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ     |

| 86     | DO[5]       | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ     |

| 87     | DO[4]       | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ     |

| 88     | PVDD2DGZ    |     |              |        |            | I/O 3.3V  |

| 89     | DO[3]       | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ     |

| 90     | DO[2]       | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ     |

| 91     | DO[1]       | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ     |

| 92     | DO[0]       | O   | 3.3V         | 8mA    | PDO08CDG   | 出力データ     |

| 93     | PVSS2DGZ    |     |              |        |            | I/O GND   |

| 94     | N.C         |     |              |        |            | N.C       |

| 95     | N.C         |     |              |        |            | N.C       |

| 96     | N.C         |     |              |        |            | N.C       |

| 97     | N.C         |     |              |        |            | N.C       |

| 98     | N.C         |     |              |        |            | N.C       |

| 99     | PVDD2DGZ    |     |              |        |            | I/O 3.3V  |

| 100    | PVDD1DGZ    |     |              |        |            | core 1.2V |

| 101    | PVSS1DGZ    |     |              |        |            | core GND  |

| 102    | PVSS2DGZ    |     |              |        |            | I/O GND   |

| 103    | N.C         |     |              |        |            | N.C       |

| 104    | N.C         |     |              |        |            | N.C       |

| 105    | N.C         |     |              |        |            | N.C       |

| 106    | N.C         |     |              |        |            | N.C       |

| 107    | N.C         |     |              |        |            | N.C       |

| 108    | PVSS2DGZ    |     |              |        |            | I/O GND   |

| 109    | DI[0]       | I   | 3.3V         |        | PDIDGZ     | 入力データ     |

| 110    | DI[1]       | I   | 3.3V         |        | PDIDGZ     | 入力データ     |

| 111    | DI[2]       | I   | 3.3V         |        | PDIDGZ     | 入力データ     |

| 112    | DI[3]       | I   | 3.3V         |        | PDIDGZ     | 入力データ     |

| 113    | PVDD2DGZ    |     |              |        |            | I/O 3.3V  |

| 114    | DI[4]       | I   | 3.3V         |        | PDIDGZ     | 入力データ     |

| 115    | DI[5]       | I   | 3.3V         |        | PDIDGZ     | 入力データ     |

| 116    | DI[6]       | I   | 3.3V         |        | PDIDGZ     | 入力データ     |

| 117    | DI[7]       | I   | 3.3V         |        | PDIDGZ     | 入力データ     |

| 118    | PVSS2DGZ    |     |              |        |            | I/O GND   |

| 119    | PVSS1DGZ    |     |              |        |            | core GND  |

| 120    | PVSS1DGZ    |     |              |        |            | core GND  |

表 2.2 130nm 版 LSI ピンアサイン (4/4)

| Pin NO | Signal Name | I/O | I/F Voltage | output | I/O Buffer | Function  |

|--------|-------------|-----|-------------|--------|------------|-----------|

| 121    | PVDD1DGZ    |     |             |        |            | core 1.2V |

| 122    | PVDD2DGZ    |     |             |        |            | I/O 3.3V  |

| 123    | DI[8]       | I   | 3.3V        |        | PDIDGZ     | 入力データ     |

| 124    | DI[9]       | I   | 3.3V        |        | PDIDGZ     | 入力データ     |

| 125    | DI[10]      | I   | 3.3V        |        | PDIDGZ     | 入力データ     |

| 126    | DI[11]      | I   | 3.3V        |        | PDIDGZ     | 入力データ     |

| 127    | PVSS2DGZ    |     |             |        |            | I/O GND   |

| 128    | PVDD1DGZ    |     |             |        |            | core 1.2V |

| 129    | DI[12]      | I   | 3.3V        |        | PDIDGZ     | 入力データ     |

| 130    | DI[13]      | I   | 3.3V        |        | PDIDGZ     | 入力データ     |

| 131    | DI[14]      | I   | 3.3V        |        | PDIDGZ     | 入力データ     |

| 132    | DI[15]      | I   | 3.3V        |        | PDIDGZ     | 入力データ     |

| 133    | PVDD2DGZ    |     |             |        |            | I/O 3.3V  |

| 134    | PVSS1DGZ    |     |             |        |            | core GND  |

| 135    | (LED[0])    |     |             |        |            | N.C       |

| 136    | (LED[1])    |     |             |        |            | N.C       |

| 137    | END_N       | O   | 3.3V        | 8mA    | PDO08CDG   | 暗号処理完了    |

| 138    | START_N     | O   | 3.3V        | 8mA    | PDO08CDG   | 暗号処理開始    |

| 139    | PVSS2DGZ    |     |             |        |            | I/O GND   |

| 140    | PVDD1DGZ    |     |             |        |            | core 1.2V |

| 141    | PVSS1DGZ    |     |             |        |            | core GND  |

| 142    | PVSS2DGZ    |     |             |        |            | I/O GND   |

| 143    | STATE[0]    | O   | 3.3V        | 8mA    | PDO08CDG   | 選択 IP を示す |

| 144    | STATE[1]    | O   | 3.3V        | 8mA    | PDO08CDG   | 選択 IP を示す |

| 145    | STATE[2]    | O   | 3.3V        | 8mA    | PDO08CDG   | 選択 IP を示す |

| 146    | STATE[3]    | O   | 3.3V        | 8mA    | PDO08CDG   | 選択 IP を示す |

| 147    | PVDD2DGZ    |     |             |        |            | I/O 3.3V  |

| 148    | PVSS1DGZ    |     |             |        |            | core GND  |

| 149    | (MON[0])    |     |             |        |            | N.C       |

| 150    | (MON[1])    |     |             |        |            | N.C       |

| 151    | (MON[2])    |     |             |        |            | N.C       |

| 152    | (MON[3])    |     |             |        |            | N.C       |

| 153    | PVSS2DGZ    |     |             |        |            | I/O GND   |

| 154    | PVDD1DGZ    |     |             |        |            | core 1.2V |

| 155    | EXEC        | O   | 3.3V        | 8mA    | PDO08CDG   | 暗号処理中     |

| 156    | N.C         |     |             |        |            | N.C       |

| 157    | N.C         |     |             |        |            | N.C       |

| 158    | N.C         |     |             |        |            | N.C       |

| 159    | PVDD2DGZ    |     |             |        |            | I/O 3.3V  |

| 160    | PVDD1DGZ    |     |             |        |            | core 1.2V |

図 2.1 130nm 版暗号 LSI ピンアサインイメージ

表 2.3 90nm 版 LSI ピンアサイン (1/4)

| Pin NO | Signal Name | I/O | I/F Voltage | output | I/O Buffer    | Function  |

|--------|-------------|-----|-------------|--------|---------------|-----------|

| 1      | PVSS1CDG_33 |     |             |        |               | core GND  |

| 2      | PVSS1CDG_33 |     |             |        |               | core GND  |

| 3      | PVSS2CDG_33 |     |             |        |               | I/O GND   |

| 4      | (SWIN[3])   |     |             |        |               | N.C       |

| 5      | (SWIN[2])   |     |             |        |               | N.C       |

| 6      | (SWIN[1])   |     |             |        |               | N.C       |

| 7      | (SWIN[0])   |     |             |        |               | N.C       |

| 8      | PVDD2POC_33 |     |             |        |               | I/O 3.3V  |

| 9      | (PHIN[1])   |     |             |        |               | N.C       |

| 10     | (PHIN[0])   |     |             |        |               | N.C       |

| 11     | N.C         |     |             |        |               | N.C       |

| 12     | N.C         |     |             |        |               | N.C       |

| 13     | PVSS2CDG_33 |     |             |        |               | I/O GND   |

| 14     | N.C         |     |             |        |               | N.C       |

| 15     | N.C         |     |             |        |               | N.C       |

| 16     | N.C         |     |             |        |               | N.C       |

| 17     | N.C         |     |             |        |               | N.C       |

| 18     | N.C         |     |             |        |               | N.C       |

| 19     | PVDD2CDG_33 |     |             |        |               | I/O 3.3V  |

| 20     | PVDD1CDG_33 |     |             |        |               | core 1.0V |

| 21     | PVSS1CDG_33 |     |             |        |               | core GND  |

| 22     | PVSS2CDG_33 |     |             |        |               | I/O GND   |

| 23     | N.C         |     |             |        |               | N.C       |

| 24     | N.C         |     |             |        |               | N.C       |

| 25     | N.C         |     |             |        |               | N.C       |

| 26     | (RSV1)      |     |             |        |               | N.C       |

| 27     | (RSV0)      |     |             |        |               | N.C       |

| 28     | PVSS2CDG_33 |     |             |        |               | I/O GND   |

| 29     | A[15]       | I   | 3.3V        |        | PDC0816CDG_33 | アドレスバス    |

| 30     | A[14]       | I   | 3.3V        |        | PDC0816CDG_33 | アドレスバス    |

| 31     | A[13]       | I   | 3.3V        |        | PDC0816CDG_33 | アドレスバス    |

| 32     | A[12]       | I   | 3.3V        |        | PDC0816CDG_33 | アドレスバス    |

| 33     | PVDD2CDG_33 |     |             |        |               | I/O 3.3V  |

| 34     | A[11]       | I   | 3.3V        |        | PDC0816CDG_33 | アドレスバス    |

| 35     | A[10]       | I   | 3.3V        |        | PDC0816CDG_33 | アドレスバス    |

| 36     | A[9]        | I   | 3.3V        |        | PDC0816CDG_33 | アドレスバス    |

| 37     | A[8]        | I   | 3.3V        |        | PDC0816CDG_33 | アドレスバス    |

| 38     | PVSS2CDG_33 |     |             |        |               | I/O GND   |

| 39     | PVSS1CDG_33 |     |             |        |               | core GND  |

| 40     | PVSS1CDG_33 |     |             |        |               | core GND  |

表 2.3 90nm 版 LSI ピンアサイン (2/4)

| Pin NO | Signal Name | I/O | I/F Volatage | output | I/O Buffer    | Function                |

|--------|-------------|-----|--------------|--------|---------------|-------------------------|

| 41     | PVDD1CDG_33 |     |              |        |               | core 1.0V               |

| 42     | PVDD2CDG_33 |     |              |        |               | I/O 3.3V                |

| 43     | A[7]        | I   | 3.3V         |        | PDC0816CDG_33 | アドレスバス                  |

| 44     | A[6]        | I   | 3.3V         |        | PDC0816CDG_33 | アドレスバス                  |

| 45     | A[5]        | I   | 3.3V         |        | PDC0816CDG_33 | アドレスバス                  |

| 46     | A[4]        | I   | 3.3V         |        | PDC0816CDG_33 | アドレスバス                  |

| 47     | PVSS2CDG_33 |     |              |        |               | I/O GND                 |

| 48     | PVDD1CDG_33 |     |              |        |               | core 1.2V               |

| 49     | A[3]        | I   | 3.3V         |        | PDC0816CDG_33 | アドレスバス                  |

| 50     | A[2]        | I   | 3.3V         |        | PDC0816CDG_33 | アドレスバス                  |

| 51     | A[1]        | I   | 3.3V         |        | PDC0816CDG_33 | アドレスバス                  |

| 52     | A[0]        | I   | 3.3V         |        | PDC0816CDG_33 | アドレスバス                  |

| 53     | PVDD2CDG_33 |     |              |        |               | I/O 3.3V                |

| 54     | PVSS1CDG_33 |     |              |        |               | core GND                |

| 55     | PVSS2CDG_33 |     |              |        |               | I/O GND                 |

| 56     | CLKB        | I   | 3.3V         |        | PDS0816CDG_33 | クロック.シミュット              |

| 57     | PVSS2CDG_33 |     |              |        |               | I/O GND                 |

| 58     | CLKA        | I   | 3.3V         |        | PDS0816CDG_33 | クロック.シミュット              |

| 59     | PVSS2CDG_33 |     |              |        |               | I/O GND                 |

| 60     | PVDD1CDG_33 |     |              |        |               | core VDD<br>(1.2V/1.0V) |

| 61     | PVSS1CDG_33 |     |              |        |               | core GND                |

| 62     | PVSS2CDG_33 |     |              |        |               | I/O GND                 |

| 63     | HRST_N      | I   | 3.3V         |        | PDS0816CDG_33 | リセット.シミュット              |

| 64     | PVSS2CDG_33 |     |              |        |               | I/O GND                 |

| 65     | WR_N        | I   | 3.3V         |        | PDC0816CDG_33 | 書き込み指示                  |

| 66     | RD_N        | I   | 3.3V         |        | PDC0816CDG_33 | 読み出し指示                  |

| 67     | PVDD2CDG_33 |     |              |        |               | I/O 3.3V                |

| 68     | PVSS1CDG_33 |     |              |        |               | core GND                |

| 69     | DO[15]      | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ                   |

| 70     | DO[14]      | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ                   |

| 71     | DO[13]      | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ                   |

| 72     | DO[12]      | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ                   |

| 73     | PVSS2CDG_33 |     |              |        |               | I/O GND                 |

| 74     | PVDD1CDG_33 |     |              |        |               | core VDD<br>(1.2V/1.0V) |

| 75     | DO[11]      | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ                   |

| 76     | DO[10]      | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ                   |

| 77     | DO[9]       | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ                   |

| 78     | DO[8]       | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ                   |

| 79     | PVDD2CDG_33 |     |              |        |               | I/O 3.3V                |

| 80     | PVDD1CDG_33 |     |              |        |               | core VDD<br>(1.2V/1.0V) |

表 2.3 90nm 版 LSI ピンアサイン (3/4)

| Pin NO | Signal Name | I/O | I/F Volatage | output | I/O Buffer    | Function      |

|--------|-------------|-----|--------------|--------|---------------|---------------|

| 81     | PVSS1CDG_33 |     |              |        |               | core GND      |

| 82     | PVSS1CDG_33 |     |              |        |               | core GND      |

| 83     | PVSS2CDG_33 |     |              |        |               | I/O GND       |

| 84     | DO[7]       | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ         |

| 85     | DO[6]       | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ         |

| 86     | DO[5]       | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ         |

| 87     | DO[4]       | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ         |

| 88     | PVDD2CDG_33 |     |              |        |               | I/O 3.3V      |

| 89     | DO[3]       | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ         |

| 90     | DO[2]       | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ         |

| 91     | DO[1]       | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ         |

| 92     | DO[0]       | O   | 3.3V         | 8mA    | PDC0816CDG_33 | 出力データ         |

| 93     | PVSS2CDG_33 |     |              |        |               | I/O GND       |

| 94     | N.C         |     |              |        |               | N.C           |

| 95     | N.C         |     |              |        |               | N.C           |

| 96     | N.C         |     |              |        |               | N.C           |

| 97     | N.C         |     |              |        |               | N.C           |

| 98     | N.C         |     |              |        |               | N.C           |

| 99     | PVDD2CDG_33 |     |              |        |               | I/O 3.3V      |

| 100    | PVDD1CDG_33 |     |              |        |               | core VDD 1.0V |

| 101    | PVSS1CDG_33 |     |              |        |               | core GND      |

| 102    | PVSS2CDG_33 |     |              |        |               | I/O GND       |

| 103    | N.C         |     |              |        |               | N.C           |

| 104    | N.C         |     |              |        |               | N.C           |

| 105    | N.C         |     |              |        |               | N.C           |

| 106    | N.C         |     |              |        |               | N.C           |

| 107    | N.C         |     |              |        |               | N.C           |

| 108    | PVSS2CDG_33 |     |              |        |               | I/O GND       |

| 109    | DI[0]       | I   | 3.3V         |        | PDC0816CDG_33 | 入力データ         |

| 110    | DI[1]       | I   | 3.3V         |        | PDC0816CDG_33 | 入力データ         |

| 111    | DI[2]       | I   | 3.3V         |        | PDC0816CDG_33 | 入力データ         |

| 112    | DI[3]       | I   | 3.3V         |        | PDC0816CDG_33 | 入力データ         |

| 113    | PVDD2CDG_33 |     |              |        |               | I/O 3.3V      |

| 114    | DI[4]       | I   | 3.3V         |        | PDC0816CDG_33 | 入力データ         |

| 115    | DI[5]       | I   | 3.3V         |        | PDC0816CDG_33 | 入力データ         |

| 116    | DI[6]       | I   | 3.3V         |        | PDC0816CDG_33 | 入力データ         |

| 117    | DI[7]       | I   | 3.3V         |        | PDC0816CDG_33 | 入力データ         |

| 118    | PVSS2CDG_33 |     |              |        |               | I/O GND       |

| 119    | PVSS1CDG_33 |     |              |        |               | core GND      |

| 120    | PVSS1CDG_33 |     |              |        |               | core GND      |

表 2.3 90nm 版 LSI ピンアサイン (4/4)

| Pin NO | Signal Name | I/O | I/F Voltage | output | I/O Buffer    | Function  |

|--------|-------------|-----|-------------|--------|---------------|-----------|

| 121    | PVDD1CDG_33 |     |             |        |               | core 1.0V |

| 122    | PVDD2CDG_33 |     |             |        |               | I/O 3.3V  |

| 123    | DI[8]       | I   | 3.3V        |        | PDC0816CDG_33 | 入力データ     |

| 124    | DI[9]       | I   | 3.3V        |        | PDC0816CDG_33 | 入力データ     |

| 125    | DI[10]      | I   | 3.3V        |        | PDC0816CDG_33 | 入力データ     |

| 126    | DI[11]      | I   | 3.3V        |        | PDC0816CDG_33 | 入力データ     |

| 127    | PVSS2CDG_33 |     |             |        |               | I/O GND   |

| 128    | PVDD1CDG_33 |     |             |        |               | core 1.0V |

| 129    | DI[12]      | I   | 3.3V        |        | PDC0816CDG_33 | 入力データ     |

| 130    | DI[13]      | I   | 3.3V        |        | PDC0816CDG_33 | 入力データ     |

| 131    | DI[14]      | I   | 3.3V        |        | PDC0816CDG_33 | 入力データ     |

| 132    | DI[15]      | I   | 3.3V        |        | PDC0816CDG_33 | 入力データ     |

| 133    | PVDD2CDG_33 |     |             |        |               | I/O 3.3V  |

| 134    | PVSS1CDG_33 |     |             |        |               | core GND  |

| 135    | (LED[0])    |     |             |        |               | N.C       |

| 136    | (LED[1])    |     |             |        |               | N.C       |

| 137    | END_N       | O   | 3.3V        | 8mA    | PDC0816CDG_33 | 暗号処理完了    |

| 138    | START_N     | O   | 3.3V        | 8mA    | PDC0816CDG_33 | 暗号処理開始    |

| 139    | PVSS2CDG_33 |     |             |        |               | I/O GND   |

| 140    | PVDD1CDG_33 |     |             |        |               | core 1.0V |

| 141    | PVSS1CDG_33 |     |             |        |               | core GND  |

| 142    | PVSS2CDG_33 |     |             |        |               | I/O GND   |

| 143    | STATE[0]    | O   | 3.3V        | 8mA    | PDC0816CDG_33 | 選択 IP を示す |

| 144    | STATE[1]    | O   | 3.3V        | 8mA    | PDC0816CDG_33 | 選択 IP を示す |

| 145    | STATE[2]    | O   | 3.3V        | 8mA    | PDC0816CDG_33 | 選択 IP を示す |

| 146    | STATE[3]    | O   | 3.3V        | 8mA    | PDC0816CDG_33 | 選択 IP を示す |

| 147    | PVDD2CDG_33 |     |             |        |               | I/O 3.3V  |

| 148    | PVSS1CDG_33 |     |             |        |               | core GND  |

| 149    | STATE[4]    |     |             |        | PDC0816CDG_33 | N.C       |

| 150    | (MON[1])    |     |             |        |               | N.C       |

| 151    | (MON[2])    |     |             |        |               | N.C       |

| 152    | (MON[3])    |     |             |        |               | N.C       |

| 153    | PVSS2CDG_33 |     |             |        |               | I/O GND   |

| 154    | PVDD1CDG_33 |     |             |        |               | core 1.0V |

| 155    | EXEC        | O   | 3.3V        | 8mA    | PDC0816CDG_33 | 暗号処理中     |

| 156    | N.C         |     |             |        |               | N.C       |

| 157    | N.C         |     |             |        |               | N.C       |

| 158    | N.C         |     |             |        |               | N.C       |

| 159    | PVDD2CDG_33 |     |             |        |               | I/O 3.3V  |

| 160    | PVDD1CDG_33 |     |             |        |               | core 1.0V |

図 2.2 90nm 版暗号 LSI ピンアサインイメージ

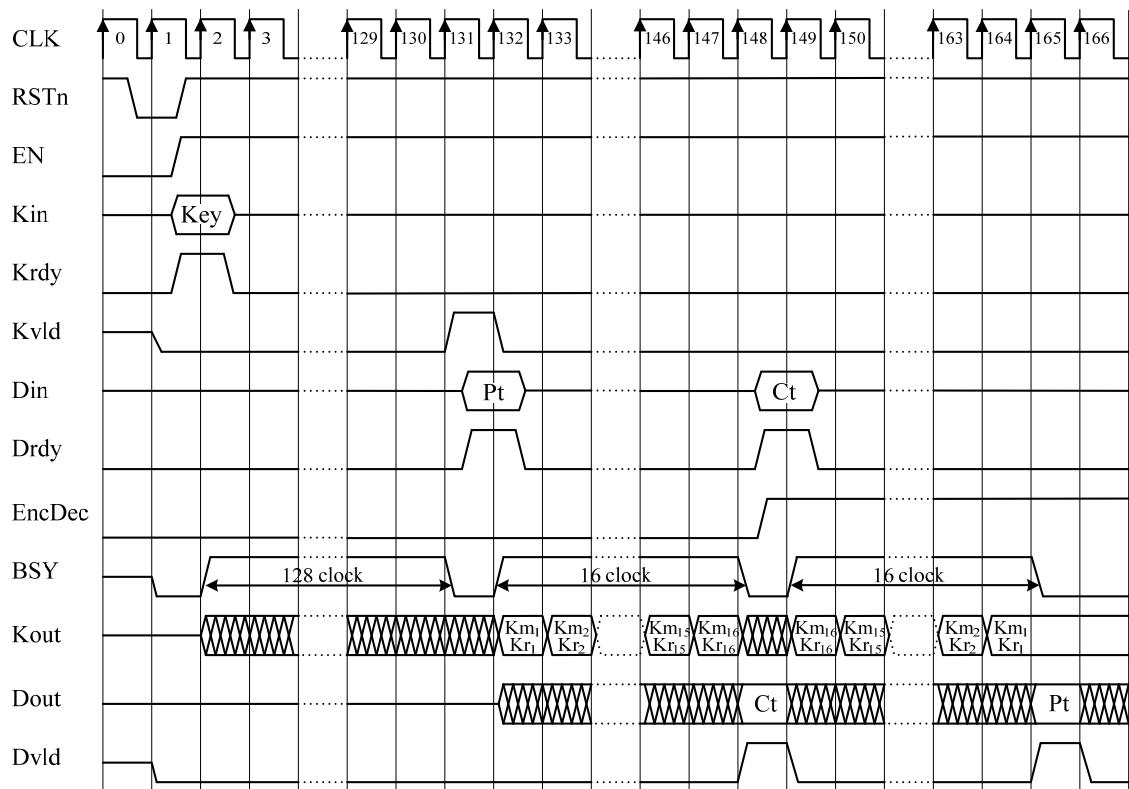

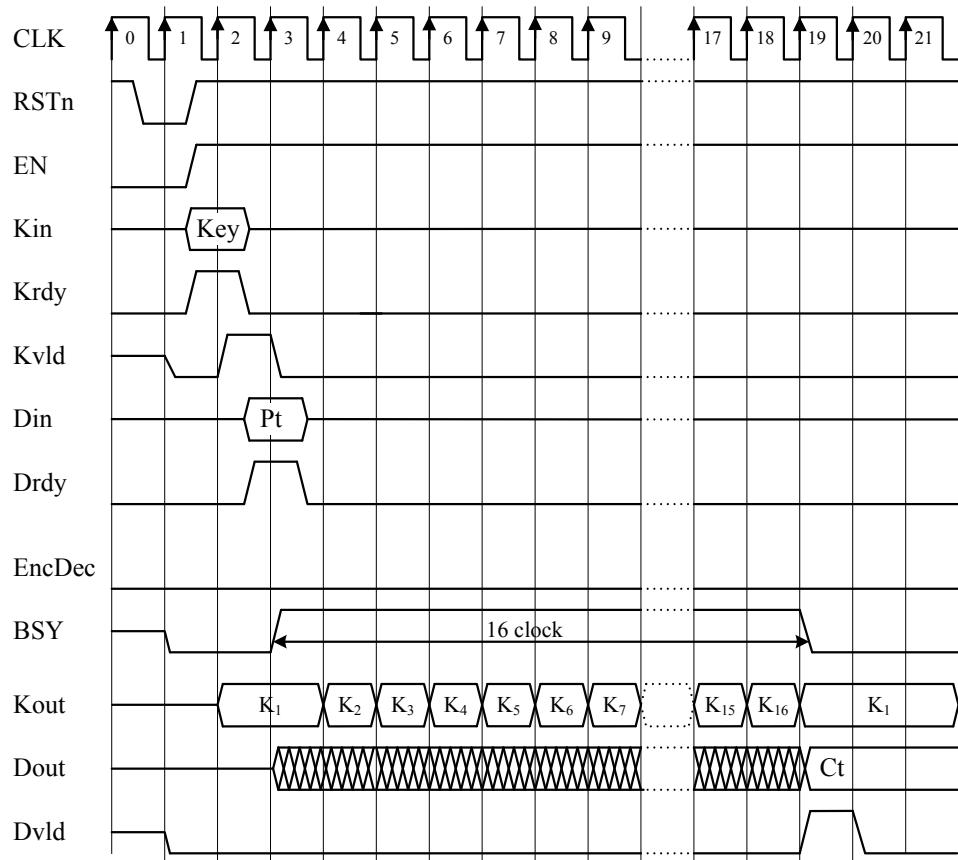

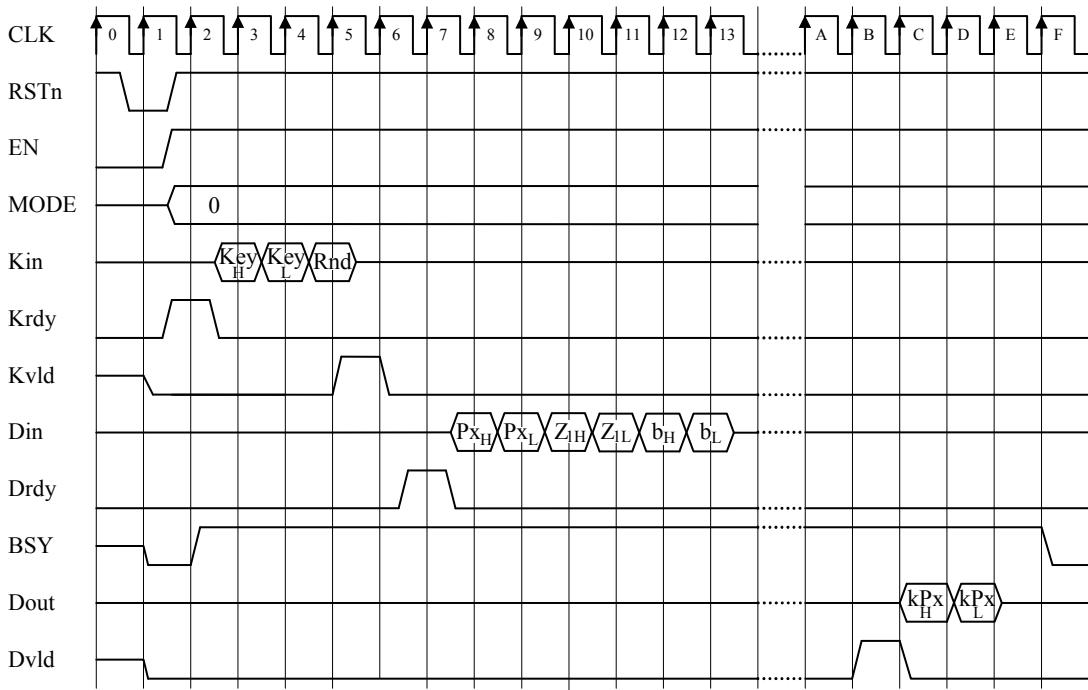

## 2.2 コマンド制御

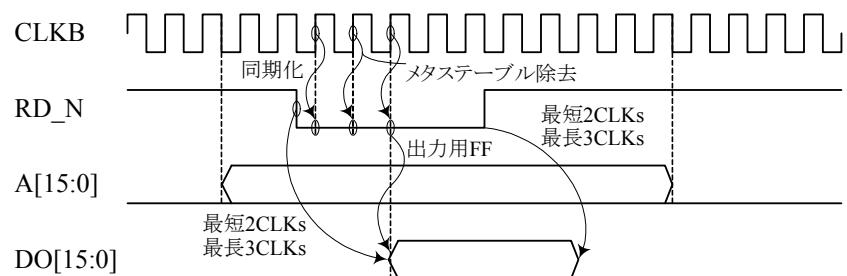

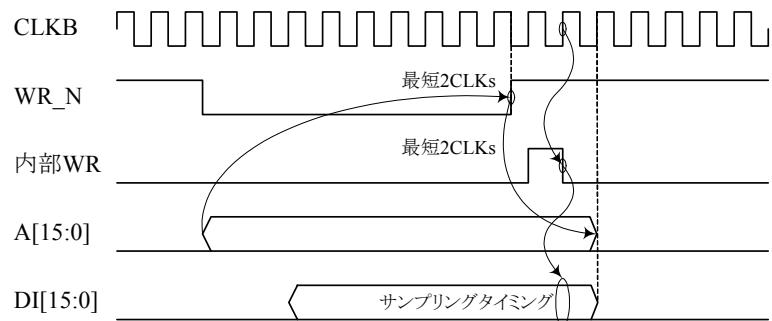

暗号 LSI のインターフェースレジスタ、及びアドレスマップ一覧を表 2.4 に、データのリード/ライト/暗号処理のタイミングを図 2.3~2.5 に示す。このインターフェースレジスタを通じて下記の手順で、各暗号 IP コアの制御を行う。インターフェースレジスタの詳細は 3.3 節を参照のこと。

- AES5 以外の暗号アルゴリズムコア

- ① 動作 IP 選択 : IP 選択レジスタ(IPSEL0, 1)の対応ビットをセット。

- ② 選択 IP リセット : CONT[IPRST]に 1 を書き込んだ後、同ビットに 0 を書き込む。

- ③ 出力 IP 選択 : 出力選択レジスタ(OUTSEL0, 1)の対応ビットをセットする。

- ④ 動作モード設定 : モードレジスタ(MODE)を設定する. (\*1)

- ⑤ 鍵設定 :

- ⑤-1 共通鍵暗号は KEY0~7, RSA は EXP0~31 と MOD0~31, ECC は IDATA0~3 を設定する。

- ⑤-2 CONT[KSET]をセットした後、同ビットがクリアされるまで待つ。

- ⑥ 初期値(IV)設定 : IV0~7 を設定する. (\*2)

- ⑦ 乱数(SEED)設定 : RAND0~7 を設定する. (\*3)

- ⑧ 暗号処理 : (以下を繰り返す)

- ⑧-1 共通鍵暗号は ITEXT0~7(\*4), RSA は IDATA0~31, ECC は IDATA8~13 を設定する.

- ⑧-2 CONT[RUN]をセットした後, 同ビットがクリアされるまで待つ.

- ⑧-3 共通鍵暗号は OTEXT0~7(\*5), RSA は ODATA0~31, ECC は ODATA0~3 を読む.

- (\*1) AES6 を選択する場合は, 必要に応じてラウンド選択レジスタ(KRSEL, DRSEL)も設定する.

(\*2) 初期値が必要な AES12, AES13 で設定する.

(\*3) 乱数を使用する AES8, AES9, AES10 で設定する.

(\*4) 64 ビットブロック暗号の場合は, ITEXT0~3 を設定する.

(\*5) 64 ビットブロック暗号の場合は, OTEXT0~3 を読み出す.

なお、AES6 選択時は、ラウンド選択レジスタに設定したラウンドもしくは fault 発生時の中間値および中間鍵(ラウンド鍵)RDATA0~7/RKEY0~7 を読み出すことが可能である。

設定を変更は以下の手順で行う。

- ・暗号コアを変更する場合は、上記①~⑧を改めて実行する.

- ・既に選択されている暗号コアの動作モード変更する場合は、上記④~⑧を改めて実行する.

- ・既に選択されている暗号コアの鍵を変更する場合は、上記⑤~⑧を改めて実行する.

- ・既に選択されている暗号コアの初期値を変更する場合は、上記⑥~⑧を改めて実行する.

- ・既に選択されている暗号コアの乱数を変更する場合は、上記⑦~⑧を改めて実行する.

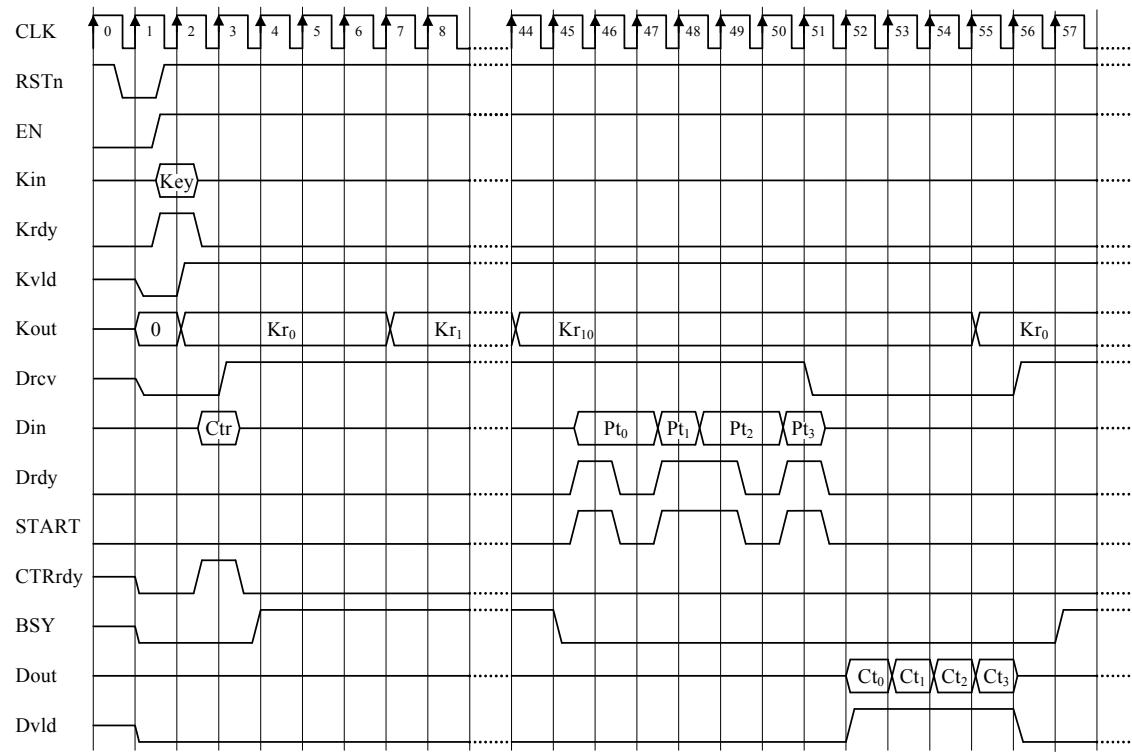

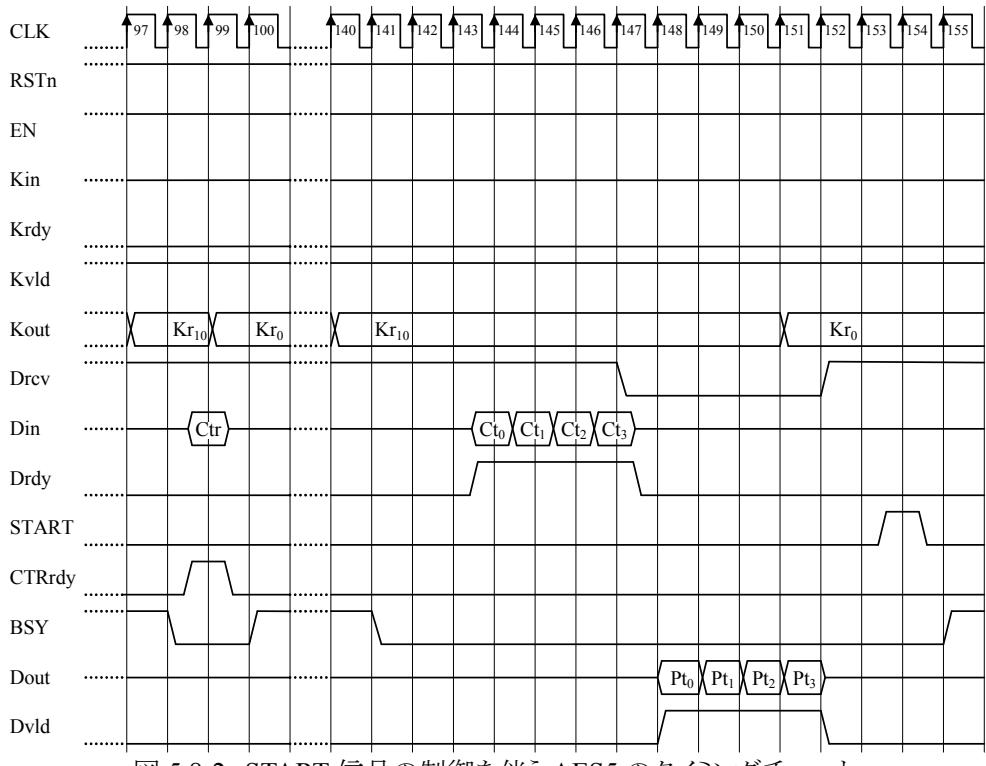

#### ● AES5(CTR モード+4 段パイプライン実装)

- ①~⑤ 上記の手順と同じ.

- ⑥ 初期値(IV)設定 :

- ⑥-1 IV0~7 を設定する.

- ⑥-2 コントロールレジスタ CONT[RUN]に 1 を書き込み後, 同ビットがクリアされるのを待つ.

- ⑦ 乱数(SEED)設定 : 設定不要

- ⑧ 暗号処理 : (以下を繰り返す)

- ⑧-1 ITEXT0~31 を設定する.

- ⑧-2 コントロールレジスタ CONT[RUN]に 1 を書き込み後, 同ビットがクリアされるのを待つ.

- ⑧-3 OTEXT0~31 を読み出す.

初期値を変更する場合は、上記⑥~⑧を改めて実行する。

表 2.4 インタフェースレジスタ (1/2)

| 分類                   | アドレス | レジスタ名         | 略称      | R/W | 機能など                                                          |

|----------------------|------|---------------|---------|-----|---------------------------------------------------------------|

| システム<br>制御           | 0000 | (予約)          |         | --  |                                                               |

|                      | 0002 | コントロールレジスタ    | CONT    | R/W | 処理開始の指示(W)/終了の通知(R)<br>鍵生成の指示(W)/終了の通知(R)<br>暗号 IP のリセット制御(W) |

|                      | 0004 | IP 選択レジスタ 0   | IPSEL0  | R/W | 動作させる暗号 IP を指定                                                |

|                      | 0006 | IP 選択レジスタ1    | IPSEL1  | R/W | 動作させる暗号 IP を指定                                                |

|                      | 0008 | 出力選択レジスタ 0    | OUTSEL0 | R/W | データ出力する暗号 IP を指定                                              |

|                      | 000A | 出力選択レジスタ 1    | OUTSEL1 |     | データ出力する暗号 IP を指定                                              |

|                      | 000C | モードレジスタ       | MODE    | R/W | 動作モード, 鍵長, 暗復号などを指定                                           |

|                      | 000E | ラウンド選択レジスタ    | RSEL    | R/W | 中間値保存ラウンド数指定                                                  |

|                      | 0010 | テストレジスタ 1     | TEST1   | R/W | カスタムコア動作制御 1                                                  |

|                      | 0012 | テストレジスタ 2     | TEST2   | R/W | カスタムコア動作制御 2                                                  |

|                      | :    |               |         |     |                                                               |

|                      | 00FE | (予約)          |         |     |                                                               |

|                      |      |               |         |     |                                                               |

| 共通<br>鍵暗号            | 0100 | 鍵レジスタ 0       | KEY0    | W   | 共通鍵暗号用鍵(最上位 16 ビット)                                           |

|                      | 0102 | 鍵レジスタ 1       | KEY1    | W   | 共通鍵暗号用鍵(KEY0 に続く 16 ビット)                                      |

|                      | :    | :             | :       | :   | :                                                             |

|                      | 010E | 鍵レジスタ 7       | KEY7    | W   | 共通鍵暗号用鍵(最下位 16 ビット)                                           |

|                      | 0110 | IV レジスタ 0     | IV0     | W   | 入力 IV(最上位 16 ビット)                                             |

|                      | 0112 | IV レジスタ 1     | IV1     | W   | 入力 IV(IV0 に続く 16 ビット)                                         |

|                      | :    | :             | :       | :   | :                                                             |

|                      | 011E | IV レジスタ 7     | IV7     | W   | 入力 IV(最下位 16 ビット)                                             |

|                      | 0120 | 入力テキストレジスタ 0  | ITEXT0  | W   | 入力テキスト(最上位 16 ビット)                                            |

|                      | 0122 | 入力テキストレジスタ 1  | ITEXT1  | W   | 入力テキスト(ITEXT0 に続く 16 ビット)                                     |

|                      | :    | :             | :       | :   | :                                                             |

|                      | 015E | 入力テキストレジスタ 31 | ITEXT31 | W   | 入力テキスト(最下位 16 ビット)                                            |

|                      | 0160 | 乱数レジスタ 0      | RAND0   | W   | 入力乱数(最上位 16 ビット)                                              |

|                      | 0162 | 乱数レジスタ 1      | RAND1   | W   | 入力乱数(RAND0 に続く 16 ビット)                                        |

|                      | :    | :             | :       | :   | :                                                             |

|                      | 016E | 乱数レジスタ 7      | RAND7   | W   | 入力乱数(最下位 16 ビット)                                              |

|                      | :    |               |         |     |                                                               |

|                      | 017E | (予約)          |         |     |                                                               |

| 出力<br>テキスト<br>(←LSI) | 0180 | 出力テキストレジスタ 0  | OTEXT0  | R   | 出力テキスト(最上位 16 ビット)                                            |

|                      | 0182 | 出力テキストレジスタ 1  | OTEXT1  | R   | 出力テキスト(OTEXT0 に続く 16 ビット)                                     |

|                      | :    | :             | :       | :   | :                                                             |

|                      | 01BE | 出力テキストレジスタ 31 | OTEXT31 | R   | 出力テキスト(最下位 16 ビット)                                            |

| 中間値<br>データ<br>(←LSI) | 01C0 | 中間値レジスタ 0     | RDATA0  | R   | 中間値データ(最上位 16 ビット)                                            |

|                      | 01C2 | 中間値レジスタ 1     | RDATA1  | R   | 中間値データ(RDATA0 に続く 16 ビット)                                     |

|                      | :    | :             | :       | :   | :                                                             |

|                      | 01CE | 中間値レジスタ 7     | RDATA7  | R   | 中間値データ(最下位 16 ビット)                                            |

| 中間鍵<br>(←LSI)        | 01D0 | 中間鍵レジスタ 0     | RKEY0   | R   | 中間鍵(最上位 16 ビット)                                               |

|                      | 01D2 | 中間鍵レジスタ 1     | RKEY1   | R   | 中間鍵(RKEY0 に続く 16 ビット)                                         |

|                      | :    | :             | :       | :   | :                                                             |

|                      | 01DE | 中間鍵レジスタ 7     | RKEY7   | R   | 中間鍵(最下位 16 ビット)                                               |

| (予約)                 | :    |               |         |     |                                                               |

|                      | 01FE | (予約)          |         |     |                                                               |

表 2.4 インタフェースレジスタ (2/2)

| 分類                  | アドレス                         | レジスタ名    | 略称           | R/W      | 機能など                          |

|---------------------|------------------------------|----------|--------------|----------|-------------------------------|

| 公開鍵暗号               | 指数・鍵<br>(←LSI)               | 0200     | 指数レジスタ 0     | EXP0     | W 指数(最上位 16 ビット)              |

|                     |                              | 0202     | 指数レジスタ 1     | EXP1     | W 指数(EXP0 に続く 16 ビット)         |

|                     |                              | :        | :            | :        | :                             |

|                     |                              | 023E     | 指数レジスタ 31    | EXP31    | W 指数(最下位 16 ビット)              |

|                     |                              | :        |              |          |                               |

|                     | 法<br>(→LSI)                  | 02FE     | (予約)         |          |                               |

|                     |                              | 0300     | 法レジスタ 0      | MOD0     | W 法(最上位 16 ビット)               |

|                     |                              | 0302     | 法レジスタ 1      | MOD1     | W 法(MOD0 に続く 16 ビット)          |

|                     |                              | :        | :            | :        | :                             |

|                     | 033E                         | 法レジスタ 31 | MOD31        | W        | 法(最下位 16 ビット)                 |

| 前処理演算結果入力<br>(→LSI) | 前処理演算結果入力<br>(→LSI)          | 0340     | 前処理結果レジスタ 0  | PREDAT0  | W 前処理演算結果(最上位 16 ビット)         |

|                     |                              | 0342     | 前処理結果レジスタ 1  | PREDAT1  | W 前処理演算結果(PREDAT0 に続く 16 ビット) |

|                     |                              | :        | :            | :        | :                             |

|                     |                              | 035E     | 前処理結果レジスタ 15 | PREDAT15 | W 前処理演算結果(最下位 16 ビット)         |

|                     |                              | :        |              |          |                               |

|                     | 入力データ<br>(→LSI)              | 03FE     | (予約)         |          |                               |

|                     |                              | 0400     | 入力データレジスタ 0  | IDATA0   | W 入力データ(最上位 16 ビット)           |

|                     |                              | 0402     | 入力データレジスタ 1  | IDATA1   | W 入力データ(IDATA0 に続く 16 ビット)    |

|                     |                              | :        | :            | :        | :                             |

|                     |                              | 043E     | 入力データレジスタ 31 | IDATA31  | W 入力データ(最下位 16 ビット)           |

|                     | 出力データ<br>(←LSI)              | :        |              |          |                               |

|                     |                              | 04FE     | (予約)         |          |                               |

|                     |                              | 0500     | 出力データレジスタ 0  | ODATA0   | R 出力データ(最上位 16 ビット)           |

|                     |                              | 0502     | 出力データレジスタ 1  | ODATA1   | R 出力データ(ODATA0 に続く 16 ビット)    |

|                     |                              | :        | :            | :        | :                             |

| (空き)                | LSI 情報<br>(0xFFFF0 ~0xFFFFF) | 053E     | 出力データレジスタ 31 | ODATA31  | R 出力データ(最下位 16 ビット)           |

|                     |                              | :        |              |          |                               |

|                     |                              | 05FE     | (予約)         |          |                               |

|                     |                              | 0600     |              |          |                               |

|                     |                              | :        |              |          |                               |

|                     |                              | FFEE     |              |          |                               |

|                     |                              | FFF0     | (予約)         |          |                               |

|                     |                              | :        |              |          |                               |

|                     |                              | FFFC     | バージョンレジスタ    | VER      | R                             |

|                     |                              | FFFE     | (予約)         | --       |                               |

図 2.3 リードサイクルのタイミングチャート

図 2.4 ライトサイクルのタイミングチャート

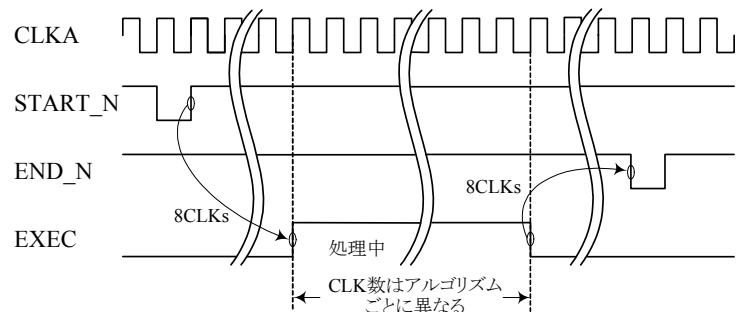

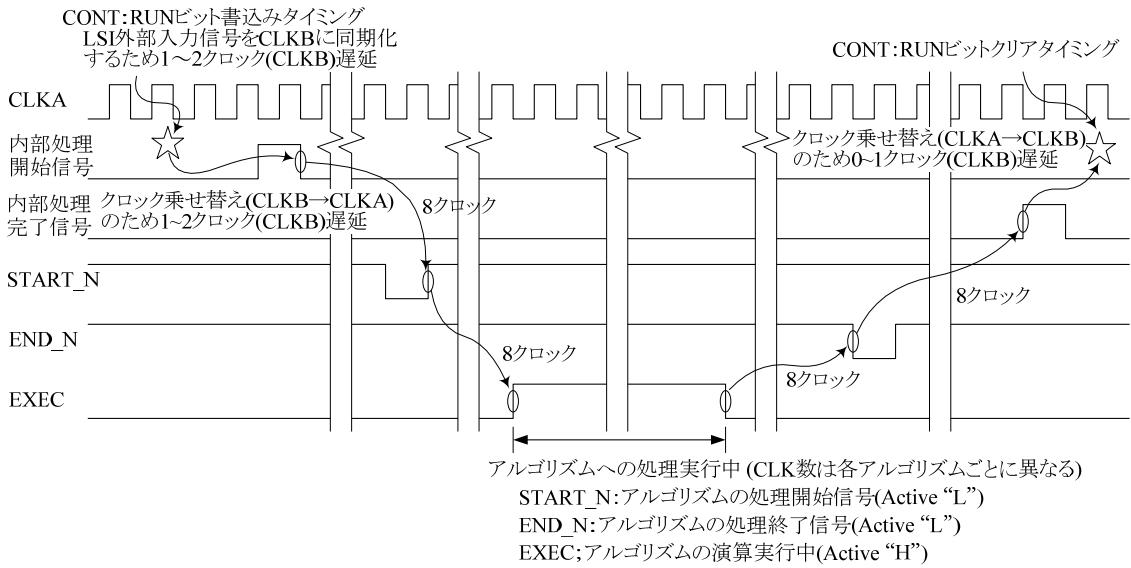

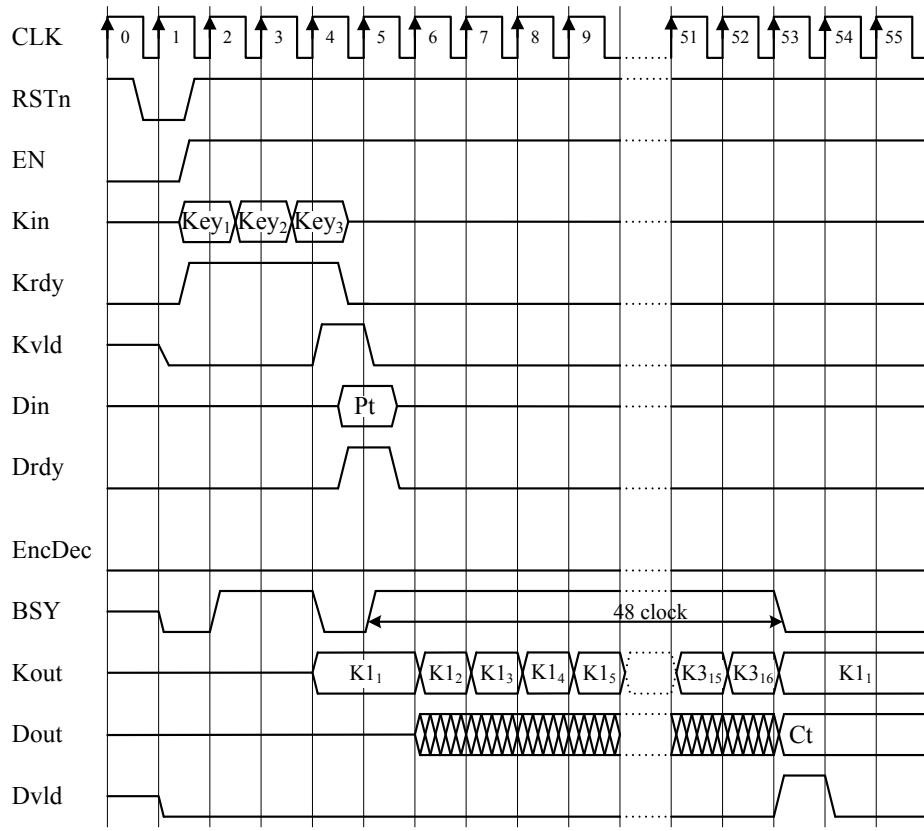

START\_N: アルゴリズムの処理開始信号(Active “L”)

END\_N: アルゴリズムの処理終了信号(Active “L”)

EXEC: アルゴリズムの演算実行中(Active “H”)

図 2.5 暗号処理のタイミングチャート

### 3 内部詳細仕様

#### 3.1 LSI 内部構成

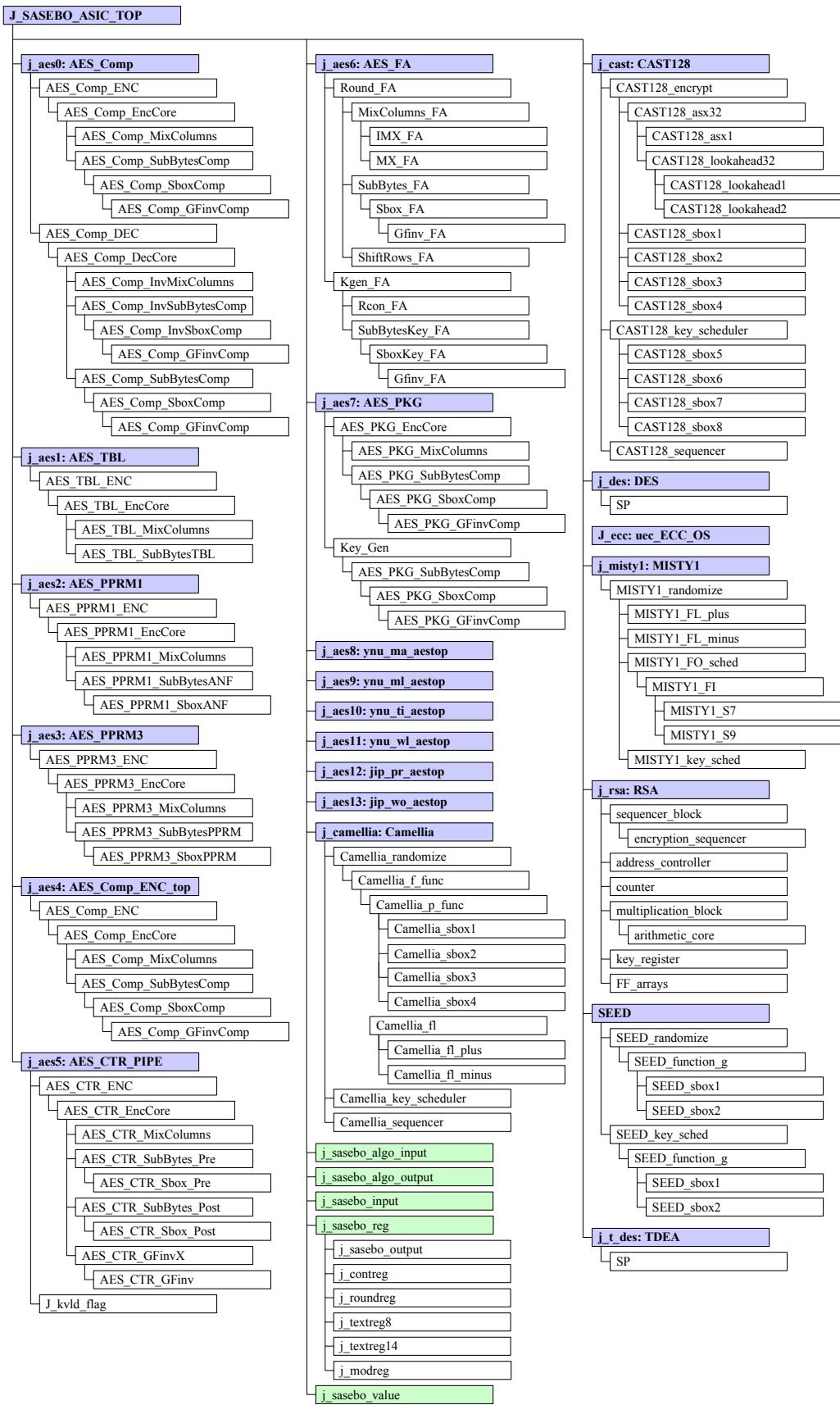

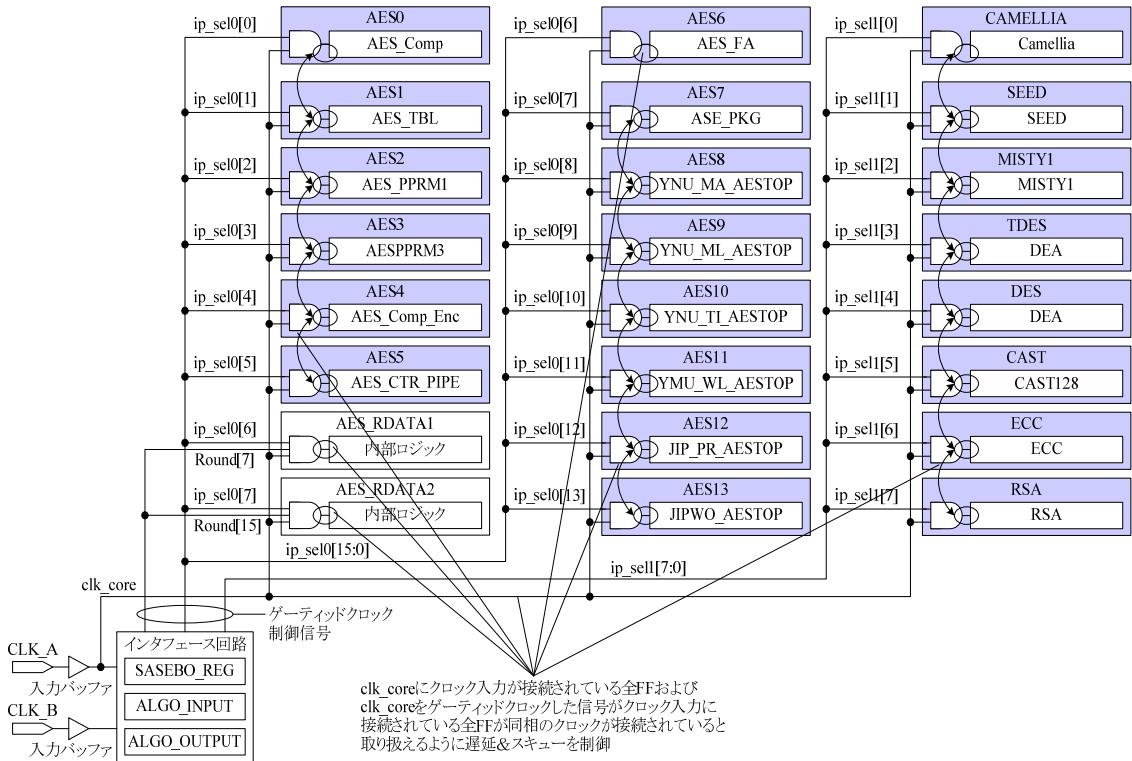

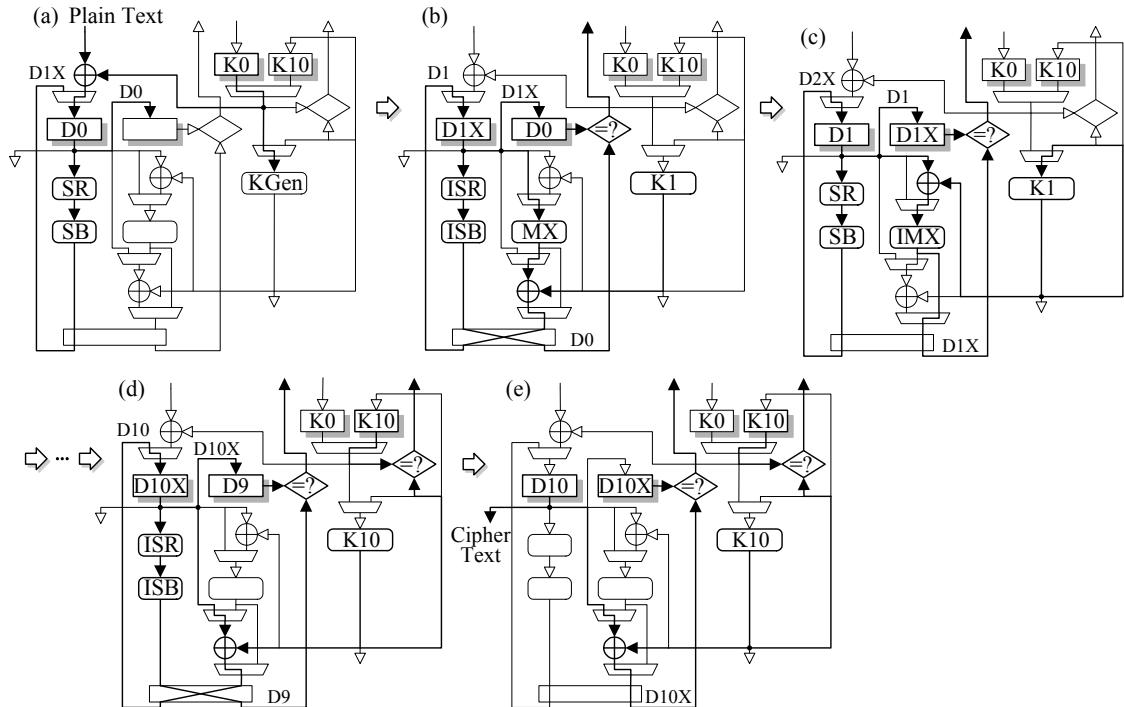

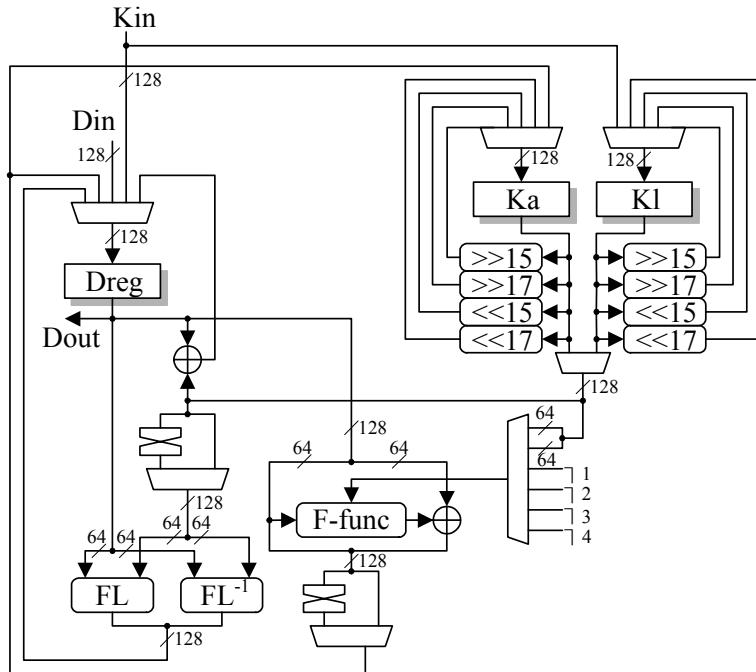

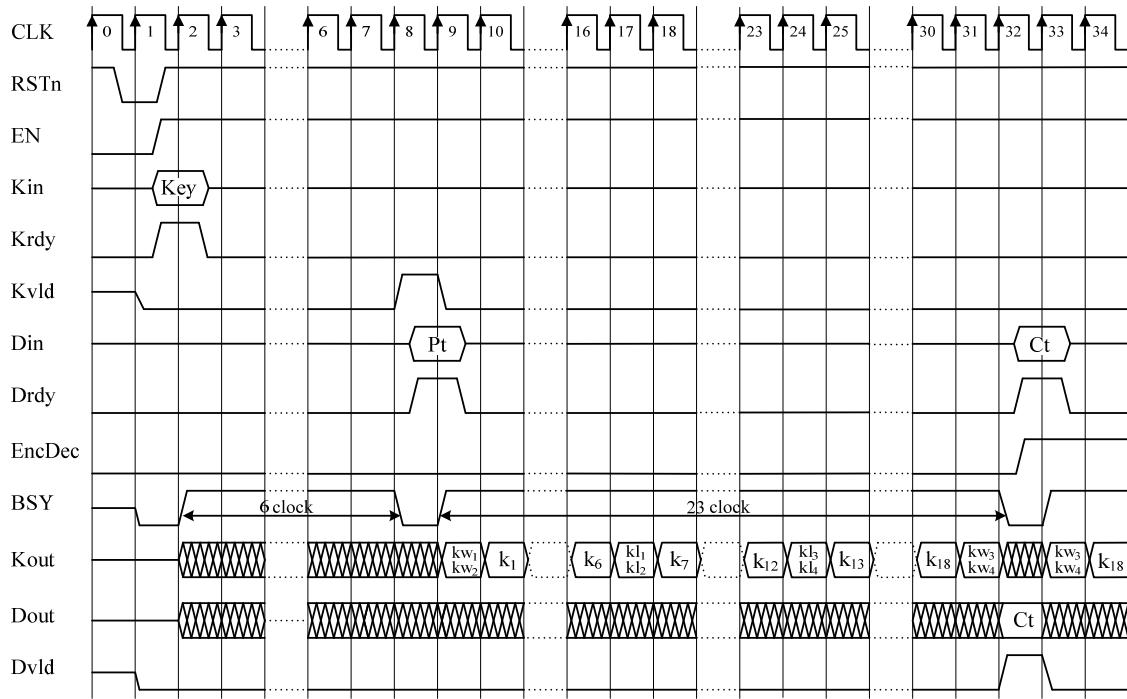

暗号 LSI の全体ブロック図を図 3.1 に、また各暗号 IP のソースコードの階層構造を図 3.2 に示す。暗号 LSI は表 3.1 の 22 種類の暗号 IP コアとインターフェース回路から構成されている。

表 3.1 暗号 IP コア

| IP No. | IP コア                        | HDL ソース Top モジュール | 内容                                                                                                |

|--------|------------------------------|-------------------|---------------------------------------------------------------------------------------------------|

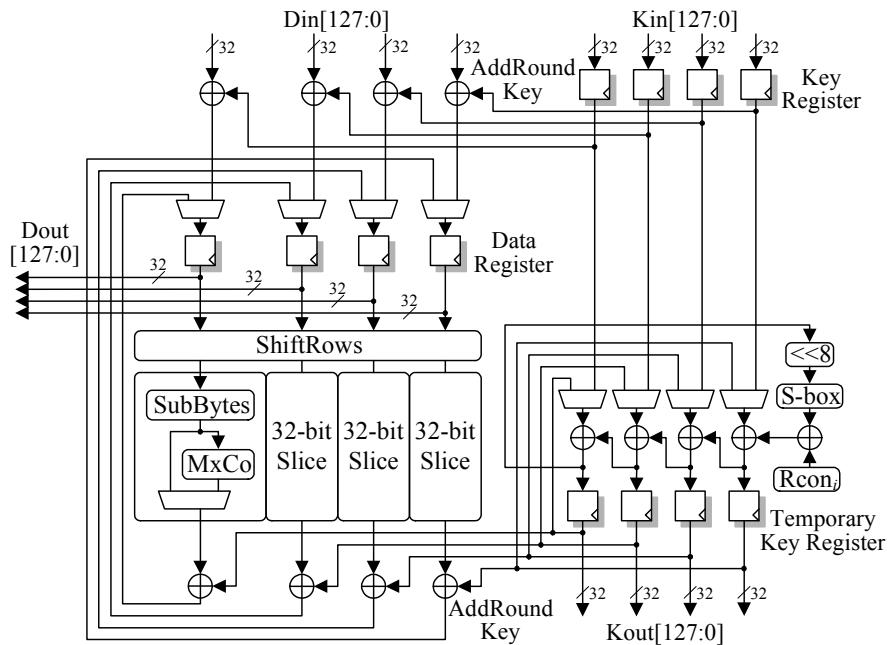

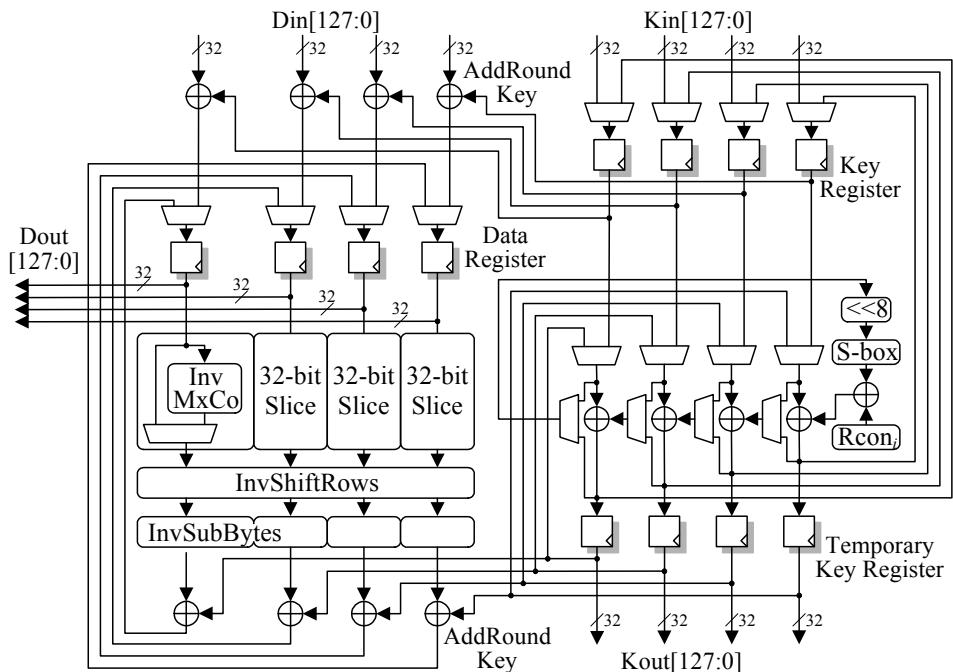

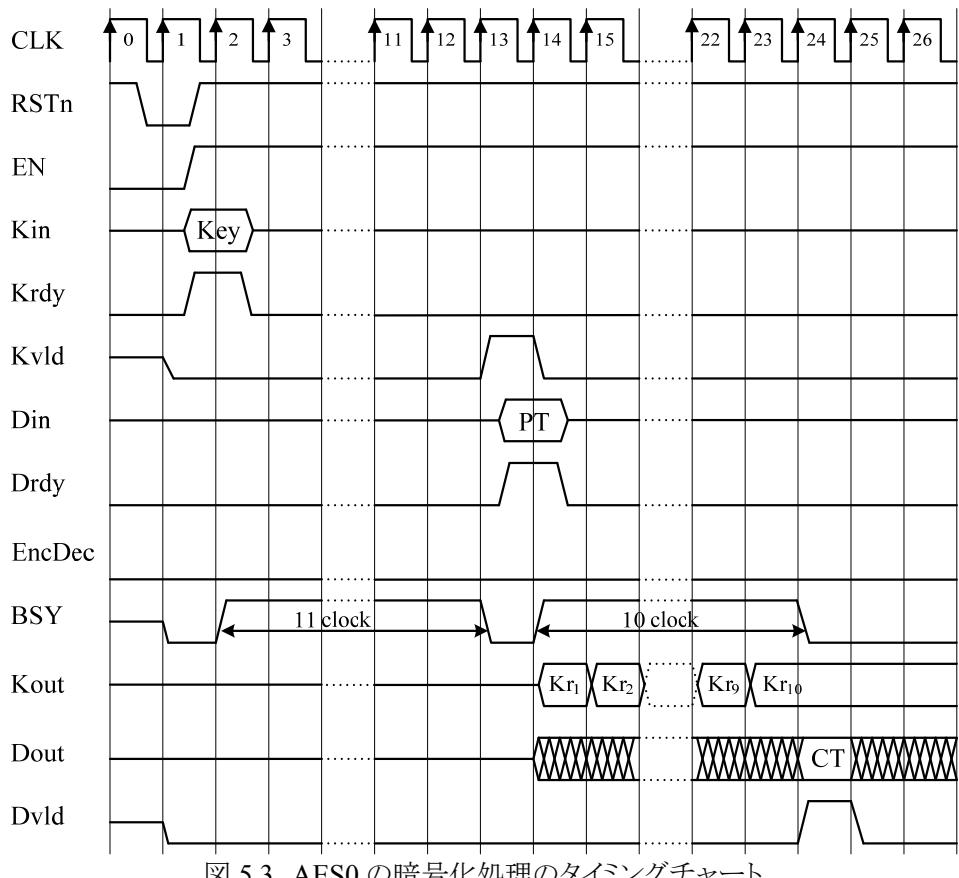

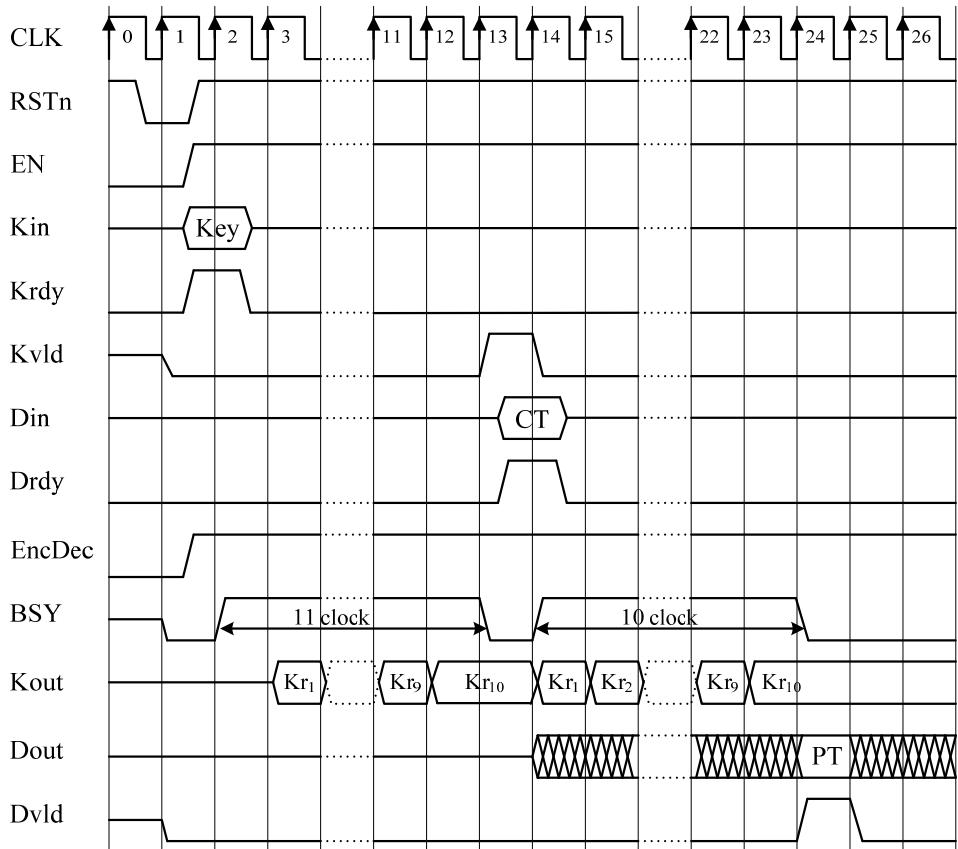

| 1      | AES0<br>(合成体 S-box)          | AES_Comp          | 合成体の S-box を用いた AES 実装。128 ビット鍵による暗号化と復号をサポート。                                                    |

| 2      | AES1<br>(テーブル S-box)         | AES_TBL           | S-box を case 文で記述したもの AES 実装。128 ビット鍵による暗号化のみサポート。                                                |

| 3      | AES2<br>(1-stage PPRM S-box) | AES_PPRM1         | Positive Prime Reed-Muler (PPRM)論理による 1 段の AND-XOR ロジックで S-box を記述した AES 実装。128 ビット鍵による暗号化のみサポート。 |

| 4      | AES3<br>(3-stage PPRM S-box) | AES_PPRM3         | PPRM 論理による 3 段の AND-XOR ロジックで S-box を記述した AES 実装。128 ビット鍵による暗号化のみサポート。                            |

| 5      | AES4<br>(合成体 S-box)          | AES_Comp_ENC_top  | AES_Comp の暗号化部のみの実装。                                                                              |

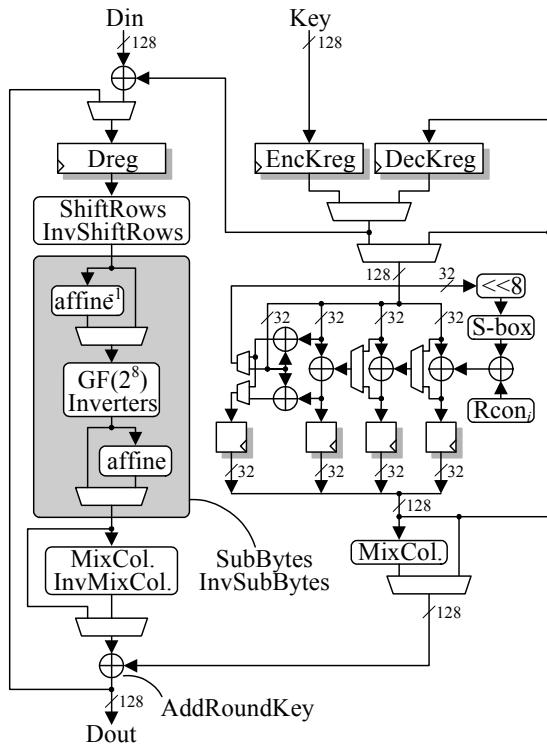

| 6      | AES5<br>(CTR モード)            | AES_CTR_PIPE      | 4 段のパイプライン実装を行った AES コアにより CTR モードをサポート。S-box は合成体を使用。                                            |

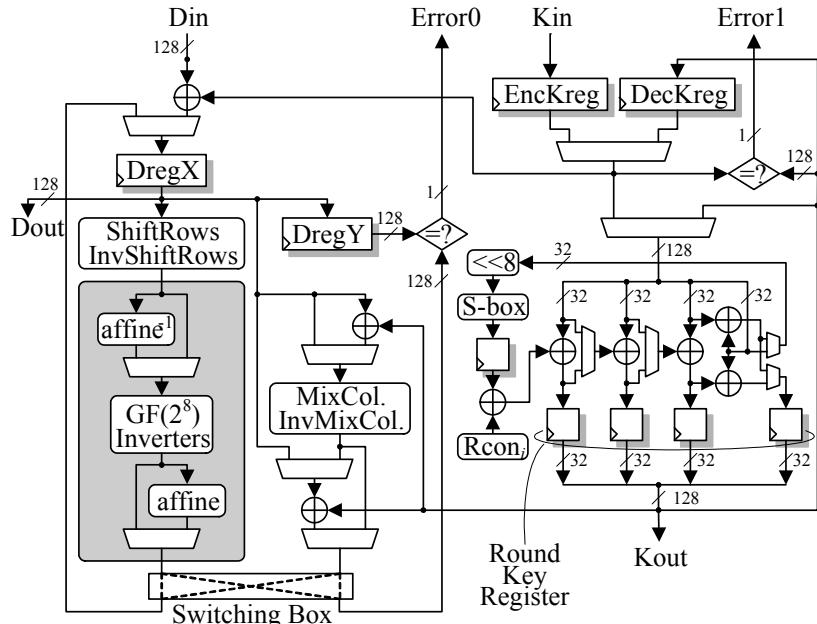

| 7      | AES6<br>(FA 対策済)             | AES_FA            | 誤動作による内部データのエラー検出を行う機構を備えた、故障利用解析攻撃(FA: Fault injection Attack)対策を実装。暗号化と復号をサポート。S-box は合成体を使用。   |

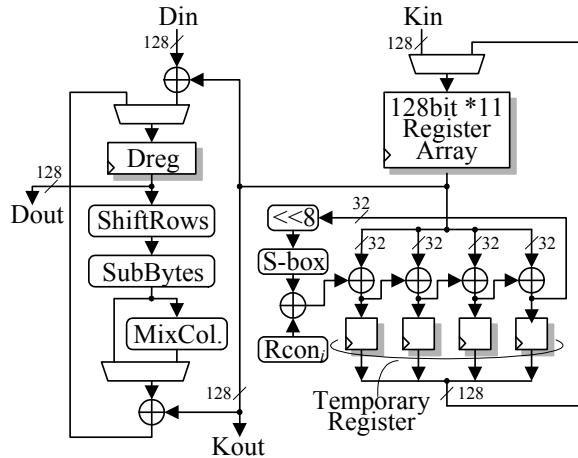

| 8      | AES7<br>(ラウンド鍵事前生成)          | AES_PKG           | 11 個のラウンド鍵を事前生成し、レジスタファイルに保存する実装。                                                                 |

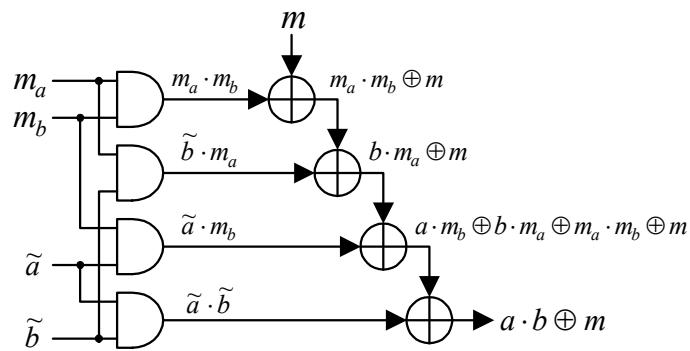

| 9      | AES8<br>(MAO)                | U_YNU_MA_AESTOP   | DPA 対策として Masked And Operation (MAO)を施した実装                                                        |

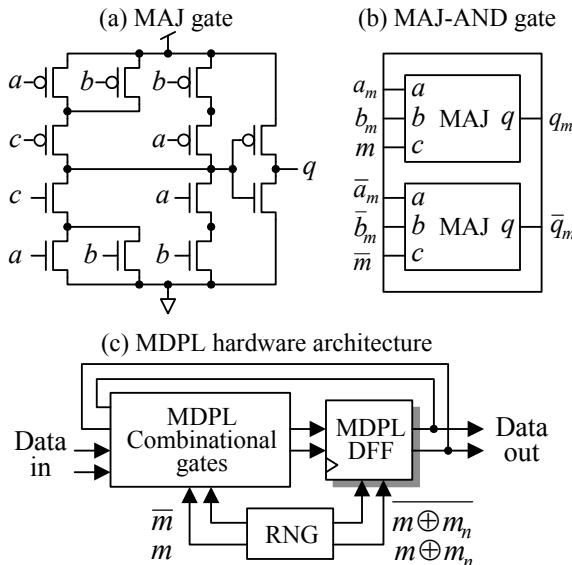

| 10     | AES9<br>(MDPL)               | U_YNU_ML_AESTOP   | DPA 対策として Masked Dual-rail Precharge Logic (MDPL)を施した実装                                           |

| 11     | AES10<br>(Threshold)         | U_YNU_TI_AESTOP   | DPA 対策として Threshold implementayion を施した実装                                                         |

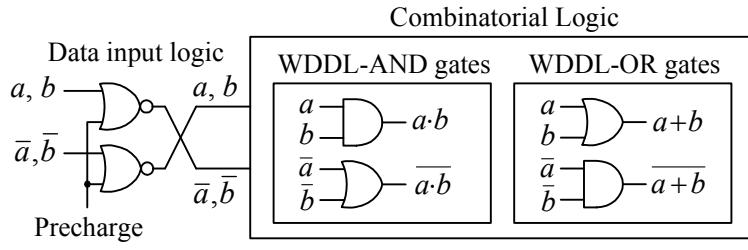

| 12     | AES11<br>(WDDL)              | U_YNU_WL_AESTOP   | DPA 対策として Wave Dynamic Differential Logic (WDDL)を施した実装                                            |

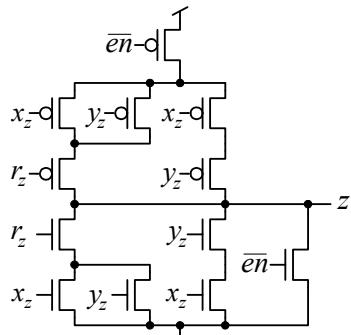

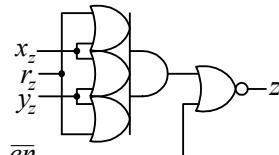

| 13     | AES12<br>(疑似 RSL)            | JIP_PR_AESTOP     | AES_Comp_Enc_top と同等の回路に、標準ライブラリで RSL(Random Switching Logic)を模擬した擬似 RSL による DPA 対策を施したもの。        |

| 14     | AES13<br>(疑似 RSL)            | JIP_WO_AESTOP     | AES_Comp と同じ RTL ソースを用い、FPGA(Xilinx Virtex2)と同等のノードを持つネットリストとなるように制約を与えて論理合成したもの。                 |

|    |          |            |                                                      |

|----|----------|------------|------------------------------------------------------|

| 15 | Camellia | Camellia   | 128 ビットブロック暗号 Camellia. S-box は case 文で記述.           |

| 16 | CAST-128 | CAST128    | 128 ビット鍵による 64 ビットブロック暗号 CAST128.                    |

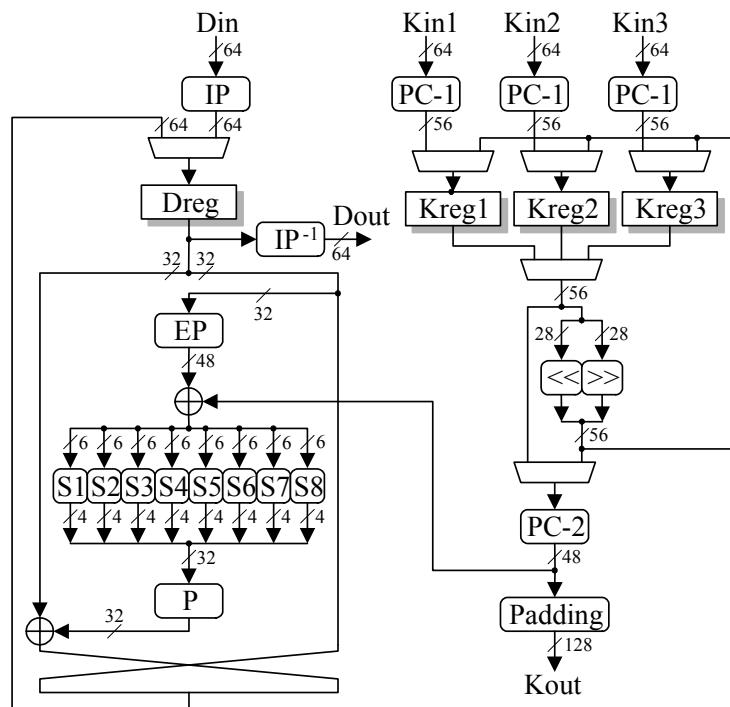

| 17 | DES      | DES        | 56 ビット鍵による 64 ビットブロック暗号の Single DES.                 |

| 18 | ECC      | Uec_ECC_OS | GF( $2^{61}$ )上の楕円曲線のスカラー倍算                          |

| 19 | MISTY1   | MISTY1     | 128 ビット鍵による 64 ビットブロック暗号. S-box S7 と S9 は case 文で記述. |

| 20 | RSA      | RSA        | 32 ビット乗算器による Montgomery 乗算を用いた RSA 暗号.               |

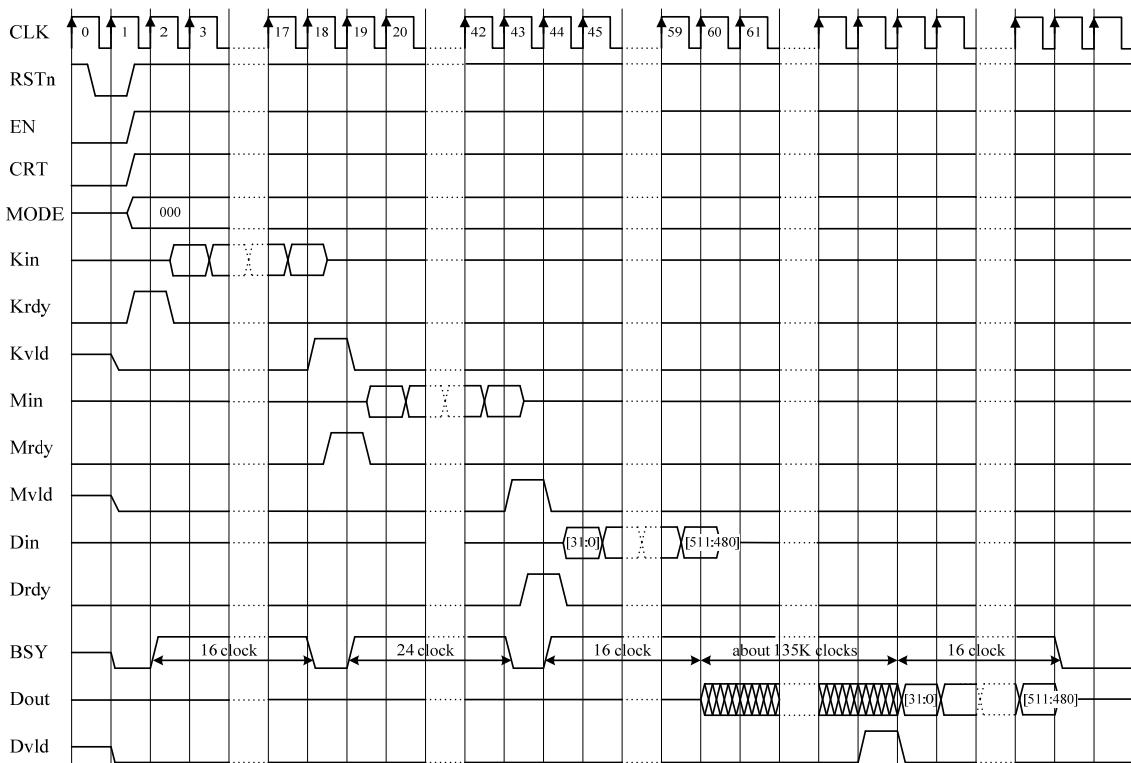

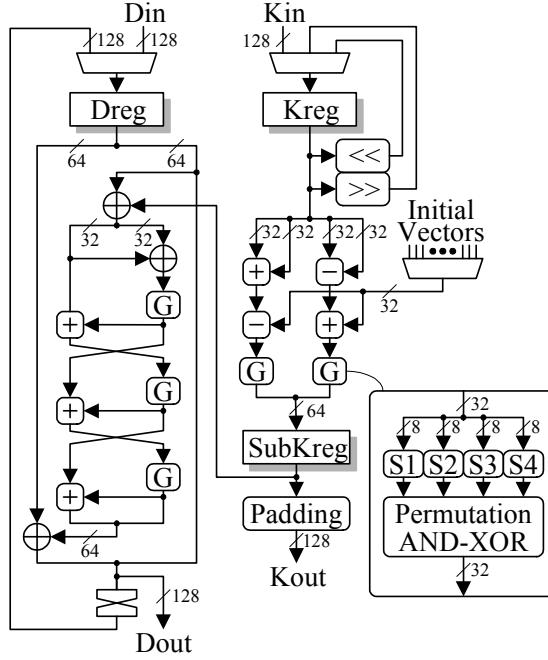

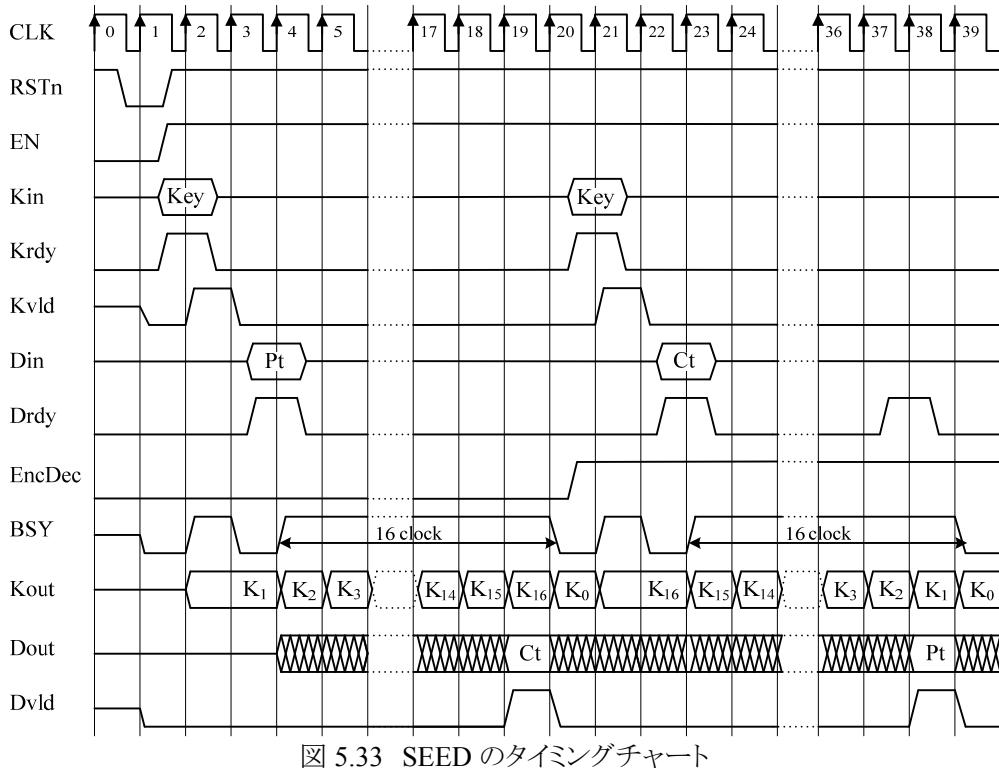

| 21 | SEED     | SEED       | 128 ビット鍵による 64 ビットブロック暗号 SEED.                       |

| 22 | TDES     | TDEA       | 3-key Triple DES                                     |

図 3.1 全体ブロック図

図 3.2 階層構造

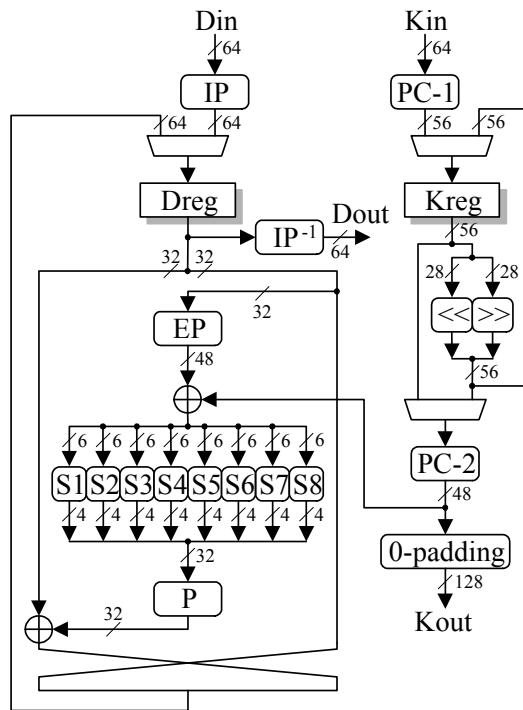

### 3.2 外部インターフェース回路

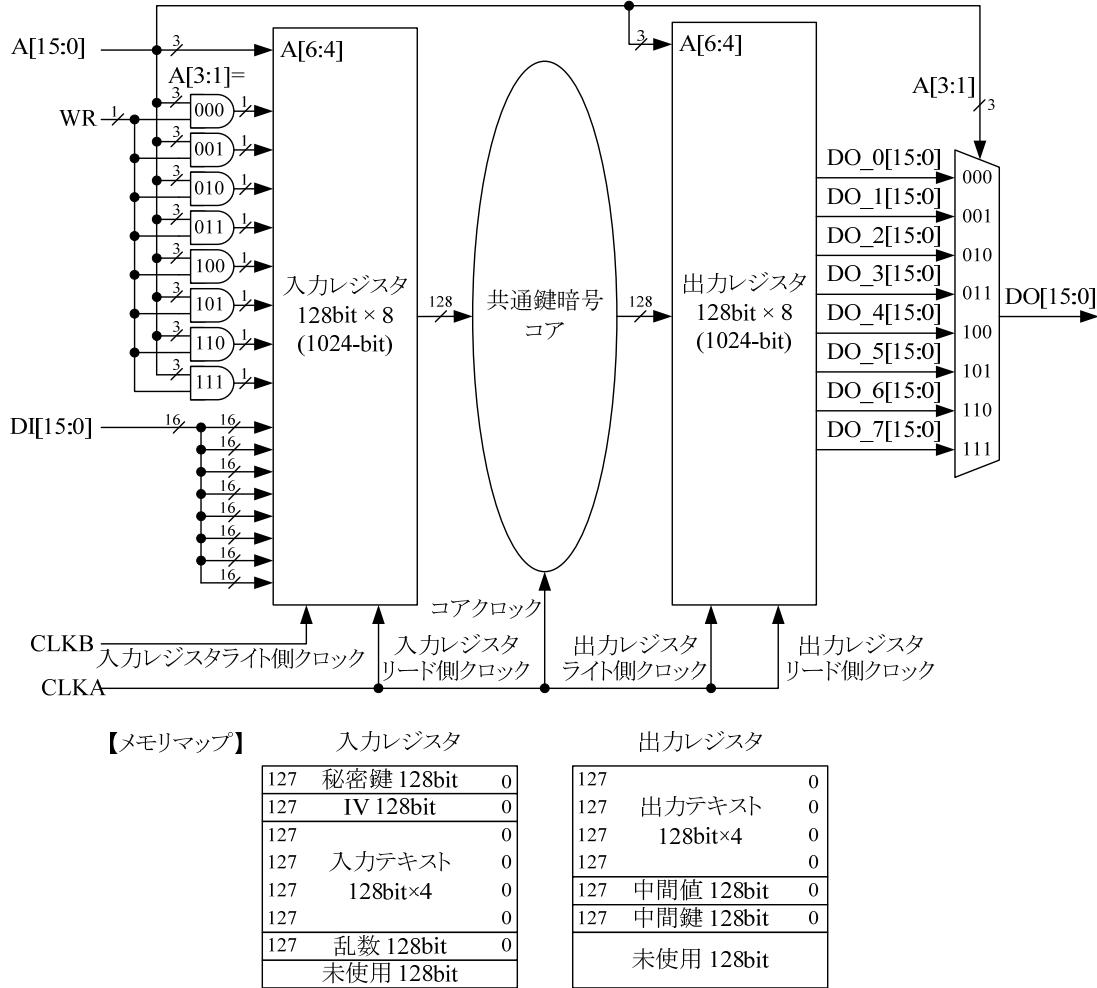

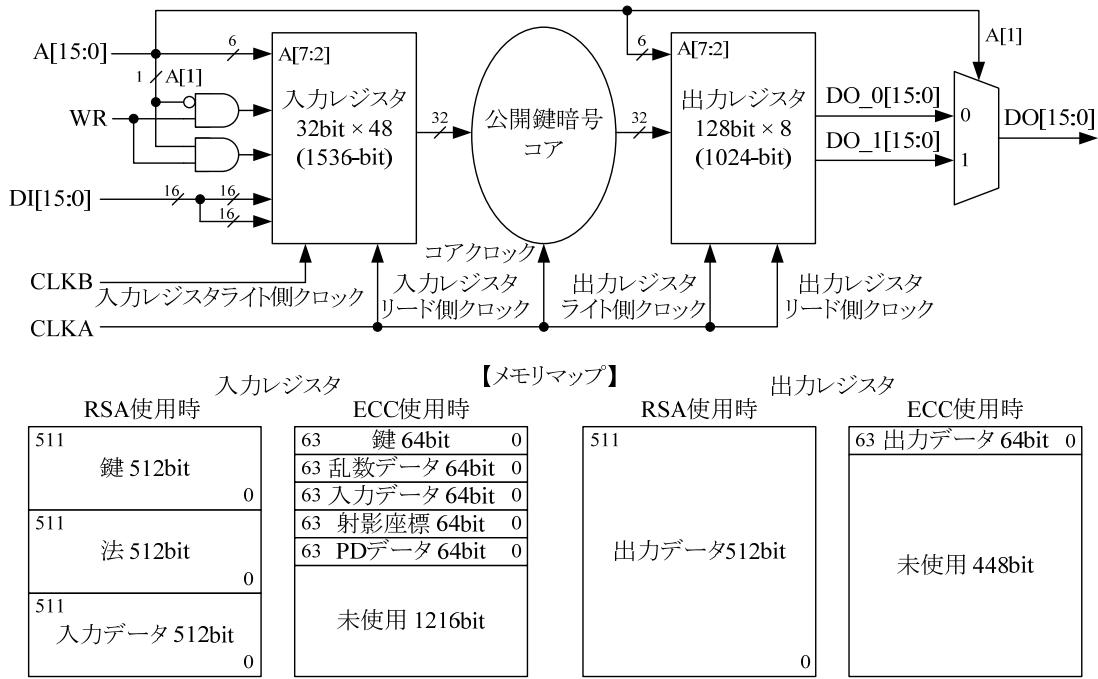

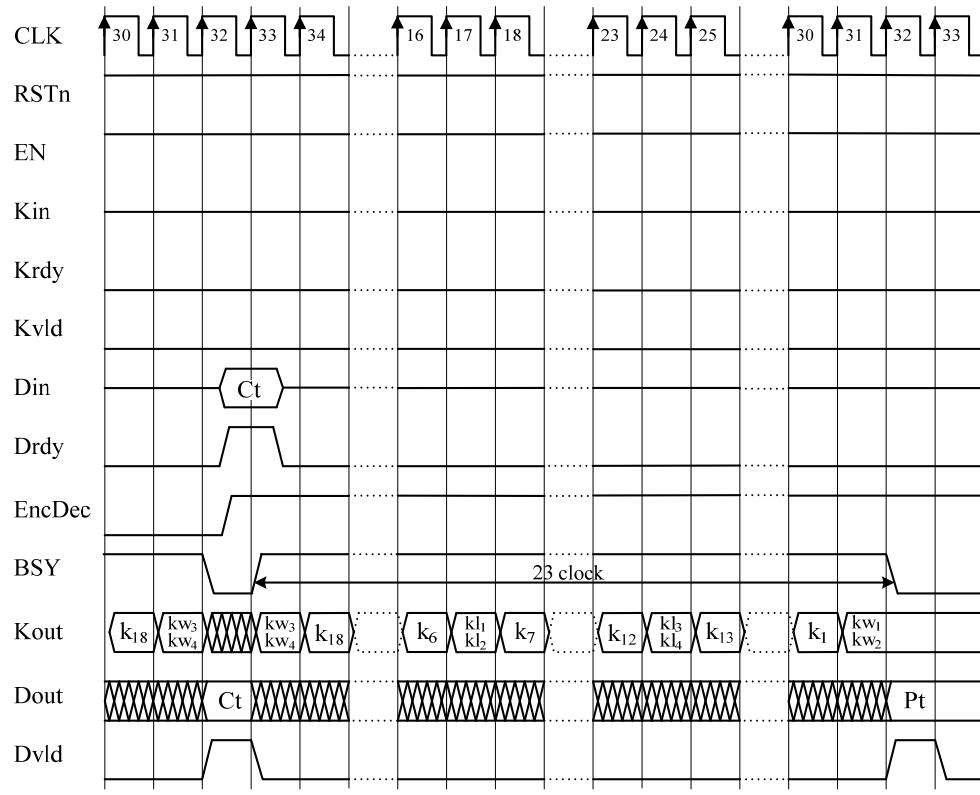

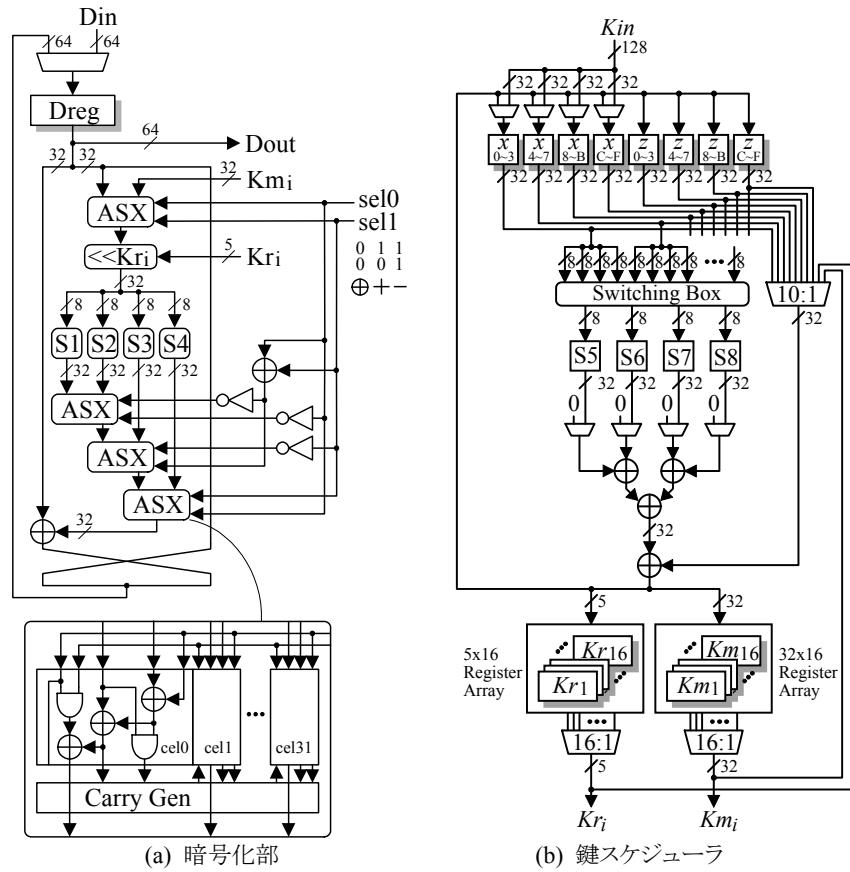

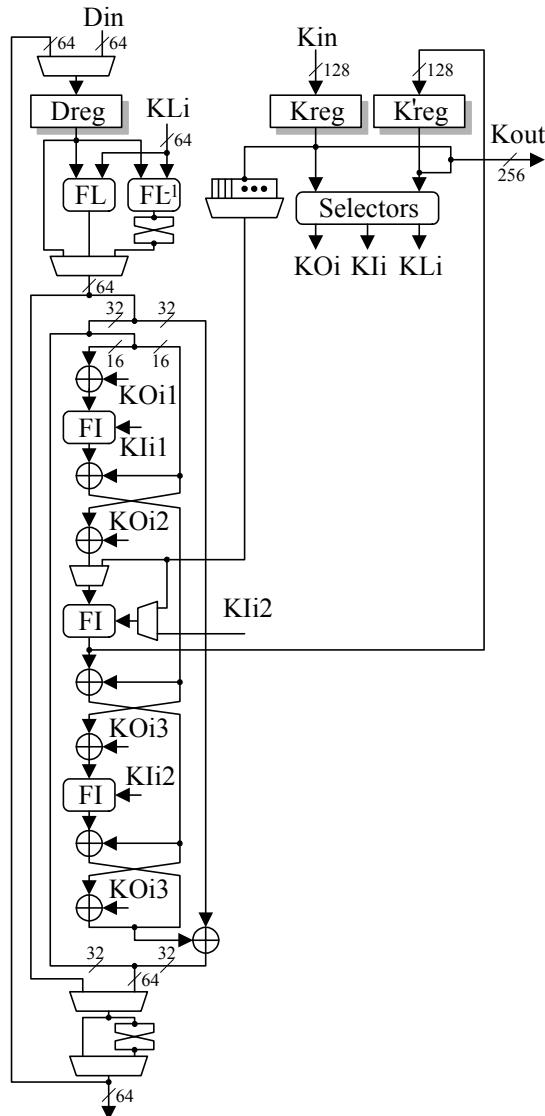

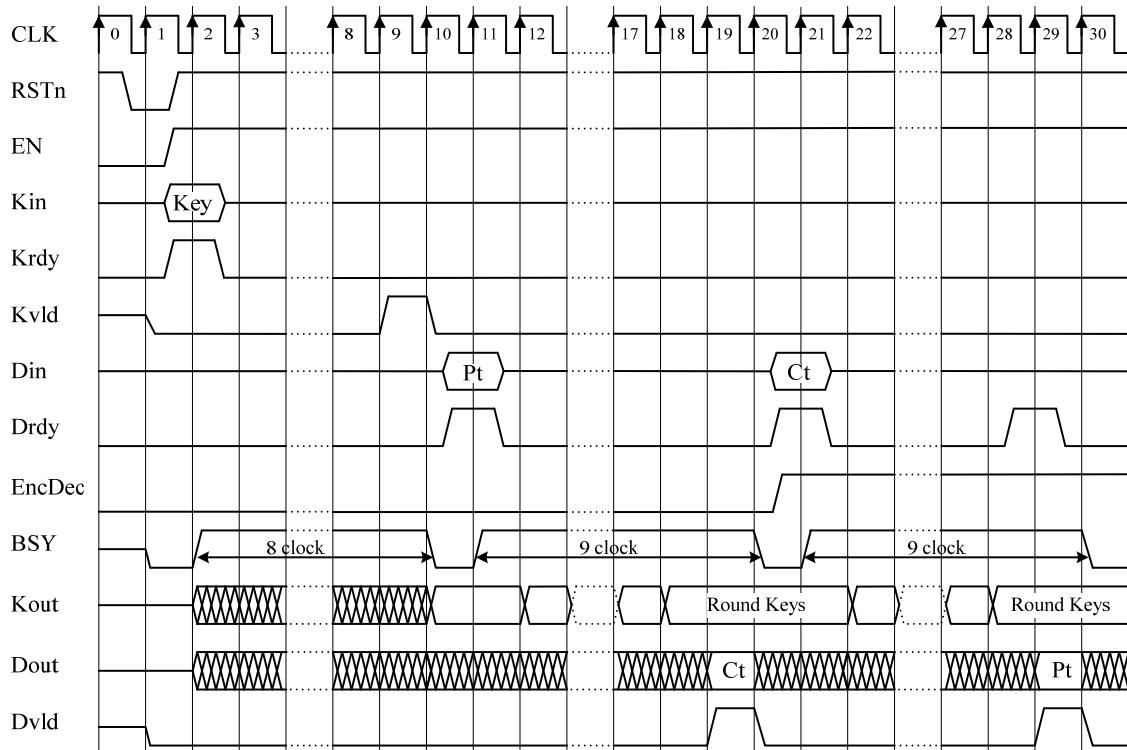

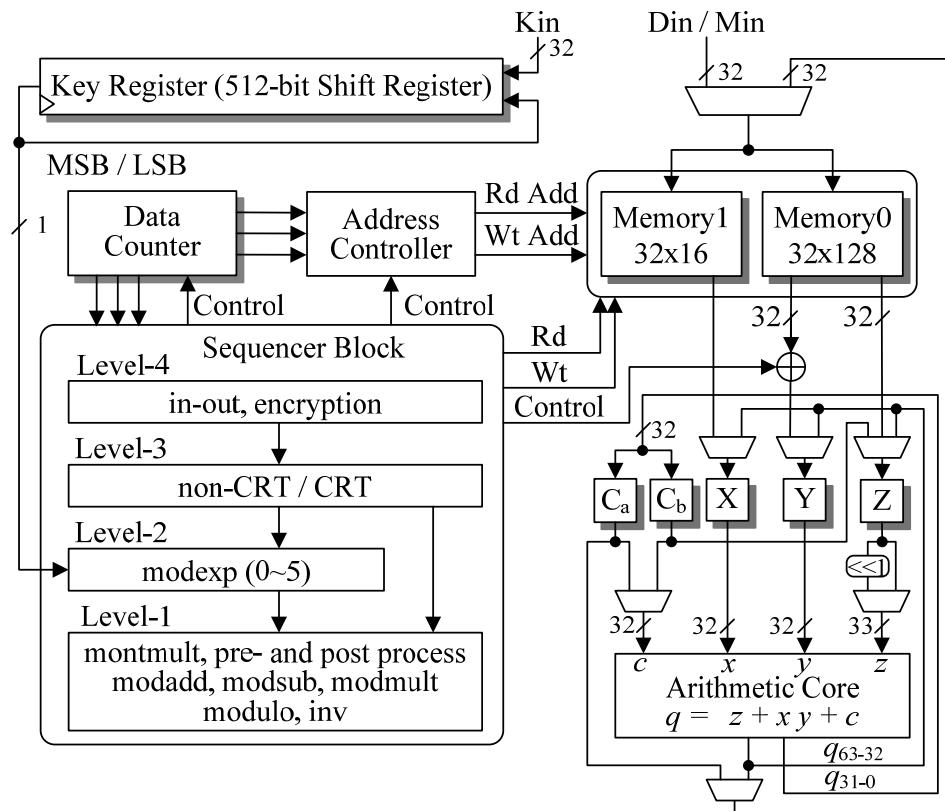

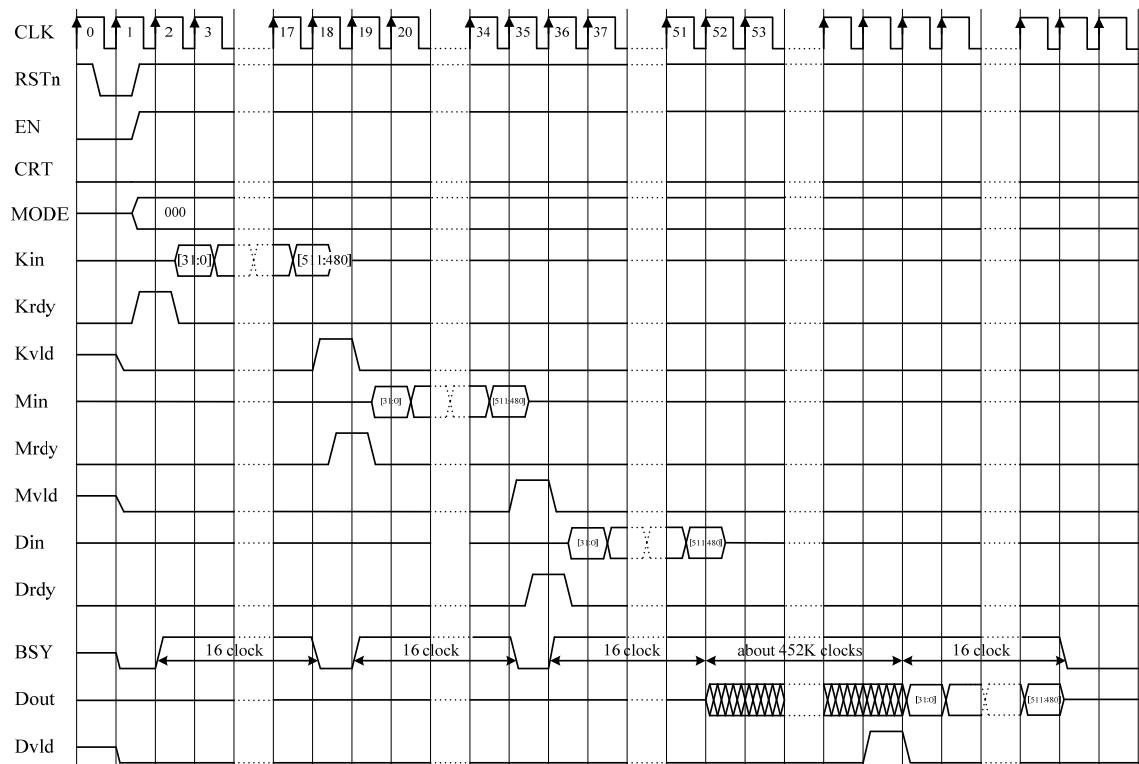

図 3.3 に共通鍵暗号(AES, DES, MISTY1, Camellia, SEED, CAST128), 図 3.4 に公開鍵暗号(RSA, ECC)の外部インターフェース回路を示す.

図 3.3 共通鍵暗号アルゴリズムのインターフェース回路

図 3.4 公開鍵暗号のインターフェース回路

### 3.3 インタフェースレジスタ

本節では各インターフェースレジスタの詳細について説明する。

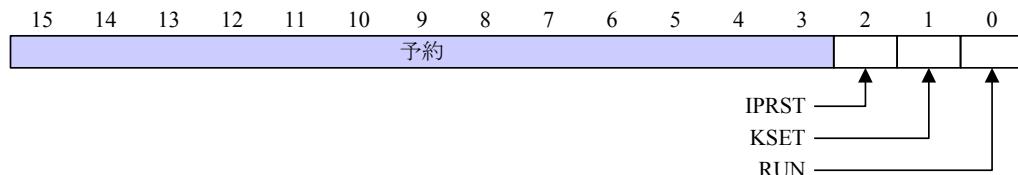

- コントロールレジスタ:CONT

本レジスタは暗号処理の開始と終了に関連する。

#### Bit 0:RUN

1 を書き込むことで、IP 選択レジスタ(IPSEL)で指定した暗号 IP が動作を開始する。内部処理では、RUNビットの情報はインテフェースクロックCLKBから内部クロックCLKAへ同期化した後、CLKAにおいて 16 クロック後に動作を開始する。出力選択レジスタ(OUTSEL)で指定した暗号 IP による処理が終了し、出力テキスト/データレジスタ(OTEXT/ODATA)の読み出しが可能になると、本ビットは自動的に 0 クリアされる。本ビットが 1 の期間中は、全てのレジスタへの書き込みは原則禁止とし、出力テキスト/データレジスタから読み出される値は無効である。

#### Bit 1:KSET

1 を書き込むことで、IP 選択レジスタ(IPSEL)で指定した暗号 IP に、モードレジスタ MODE に応じた鍵生成(鍵設定)が行われる。出力選択レジスタ(OUTSEL)で指定した暗号 IP の鍵生成(鍵設定)が終了し、設定された鍵を用いた暗号処理が可能になると、本ビットは自動的に 0 クリアされる。本ビットが 1 の期間中は、全てのレジスタへの書き込みは原則禁止とする。特に、本ビットが 1 の期間中に RUN ビットをセットした場合の動作は保証されない。

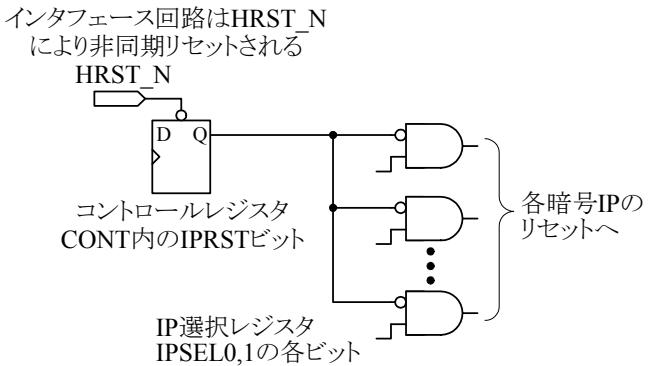

### Bit 2:IPRST

1を書き込むことで、IP選択レジスタ(IPSEL)で指定した暗号IPをリセットする。0を書き込むことで、同上の暗号IPのリセットを解除する。本ビットの初期値は1である。

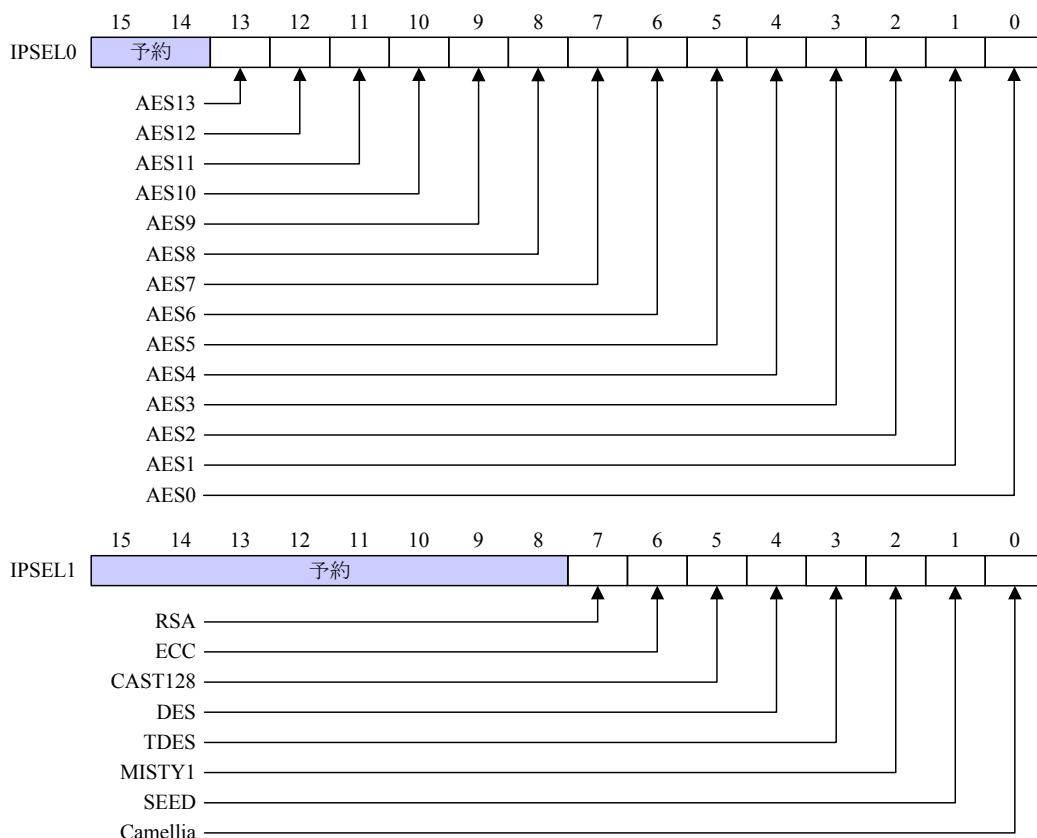

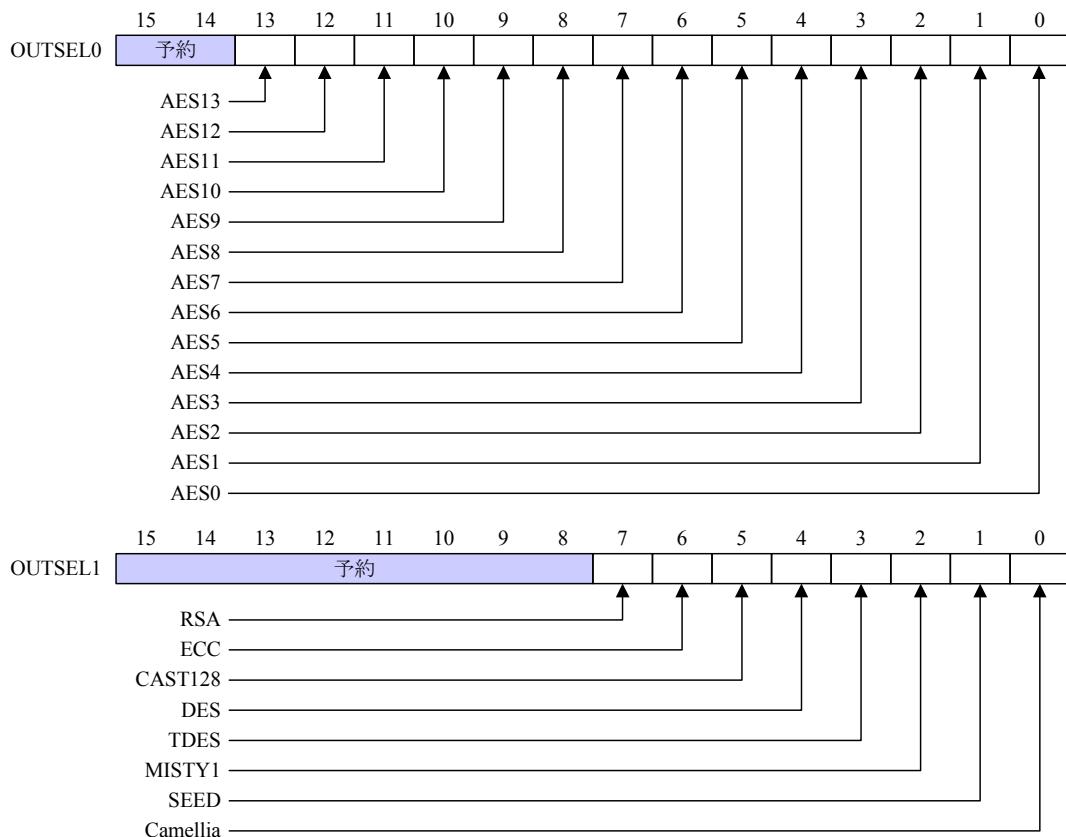

### ● IP選択レジスタ:IPSEL

22個の暗号IPのうち、IP選択レジスタの対応するビットに1がセットされたものだけがactive状態となり、選択IP以外にはクロックは供給されない。

### ● 出力選択レジスタ:OUTSEL

IP選択レジスタ(IPSEL)の対応するビットに1をセットすることで、active状態となった暗号IPのうち演算結果を出力する暗号IPを指定する。出力選択レジスタの対応するビットに1がセットされた暗号IPの演算結果が、出力テキスト/データレジスタ(OTEXT/ODATA)に格納される。出力選択レジスタの複数のビットに1をセットした場合の出力値は保証されない。

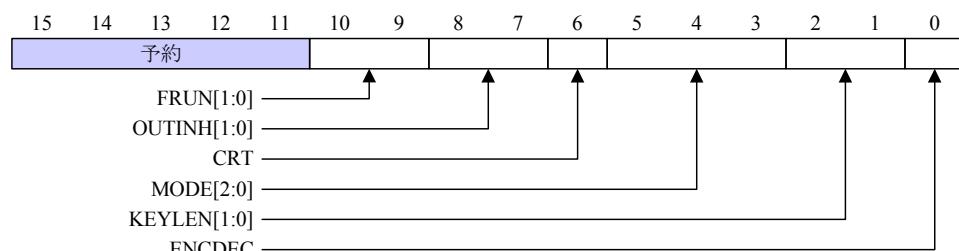

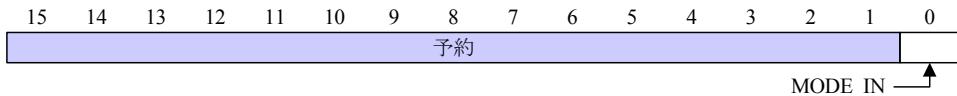

### ● モードレジスタ:MODE

動作モード, 鍵長, 暗号化/復号を指定する.

#### Bit 10-9:FRUN

AES0 のみがサポートする 0.3 秒に 1 回自動実行するフリーランモード制御

|          |   |                 |

|----------|---|-----------------|

| FRUN[1]: | 0 | フリーランモードモード OFF |

|          | 1 | フリーランモードモード ON  |

|          |   |                                 |

|----------|---|---------------------------------|

| FRUN[0]: | 0 | ITEXT を初期値に+1 インクリメントしながらフリーラン  |

|          | 1 | ITEXT を初期値に暗号化結果を次回入力にしながらフリーラン |

#### Bit 8-7:OUTINH

制御信号の出力抑止制御

|            |   |                                 |

|------------|---|---------------------------------|

| OUTINH[1]: | 0 | 制御信号出力抑止機能 OFF(制御信号は出力される)      |

|            | 1 | 制御信号出力抑止機能 ON(内容は OUTINH[0]による) |

|            |   |                      |

|------------|---|----------------------|

| OUTINH[0]: | 0 | 全ての制御信号出力を抑止         |

|            | 1 | START 信号を除く制御信号出力を抑止 |

#### Bit 6:CRT

RSA 以外の IO では意味を持たない. 本ビットは RSA コアの CRT ポートに直結される.

なお現在の LSI の CRT モードはデータによっては正しく動作しないバグが存在する.

0: CRT 处理 OFF

1: CRT 处理 ON

#### Bit 5-3:MODE[2:0]

RSA 利用時にはこのビットが RSA の MODE 入力に直結し, 値に応じて下記の処理を行う. ECC コアにも 3 ビットの動作モード制御ビットがあるが, インタフェース回路では 3'b000 に固定しており, この MODE ビットは使われない. 共通鍵暗号に対する動作モードは, AES12 がレジスタ TEST2(仕様非公開)を利用し, それ以外の暗号マクロの暗号利用モードまたは動作モードは IP 毎に固定されている.

000:左バイナリ法

001:右バイナリ法

010:対策版左バイナリ

011:対策版右バイナリ法

100:Montgomery Powering Ladder

101:M.Joye の右バイナリ法

#### Bit 2-1:KEYLEN[1:0]

値は 00 に固定されており, IP 每に決まっている鍵長が用いられる.

#### Bit 0:ENCDEC

0 で暗号化, 1 で復号を行う. 暗号化のみの IP が選択された場合, このビットは意味を持たない.

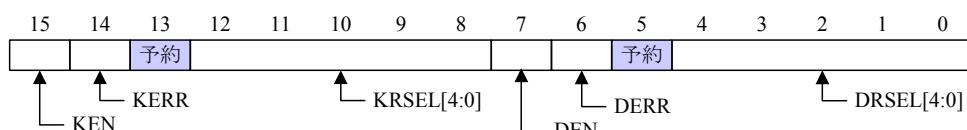

### ● ラウンド選択レジスタ:RSEL

中間値レジスタ(RDATA0~7)および中間鍵レジスタ(RKEY0~7)に値を取り込むラウンド数を指定する. DRSEL, RDATA0~7 および KRSEL, RKEY0~7 は, active な暗号 IP として故障利用解析攻撃対策が施された AES6 が選択されているときだけ意味を持つ.

#### Bit 15:KEN

0: 中間鍵を取り込むための回路の動作を抑制する(クロックを供給しない).

1: 中間鍵を取り込むための回路を活性化する(クロックを供給する).

#### Bit 14:KERR:鍵データエラーステータス(AES\_FA の Err[0]に直結)

0: 正常動作

1: エラー発生

#### Bit 12~8:KRSEL[4:0]

中間鍵レジスタ(RKEY0~7)に中間鍵データを格納すべきラウンド数.

#### Bit 7:DEN

0: 中間値を取り込むための回路の動作を抑制する(クロックを供給しない).

1: 中間値を取り込むための回路を活性化する(クロックを供給する).

#### Bit6:DERR

データエラーステータス(AES\_FA の Err[1]に直結)

0: 正常動作

1: エラー発生

#### Bit 4~0:DRSEL[4:0]

中間値レジスタ(RDATA0~7)に中間値データを格納すべきラウンド数.

### ● テストレジスタ 1:TEST1

テストレジスタ TEST1 の Bit0 に 1 をセットすることで、外部から入力した鍵の代わりに内部鍵(非公開)を使用した暗号化が行われる。一度 TEST1 がセットされると、外部からの入力鍵を使用する通常の暗号処理に戻るために、電源を落とすかハードウェアリセット HRST\_N をかける必要がある。このモードは 14 種類の全ての AES 暗号 IP コアがサポートしている。

### ● テストレジスタ 2:TEST2

テストレジスタ TEST2 は疑似 RSL 対策版 AES コア AES12 の制御を行うデバッグ用レジスタである。仕様は非公開とする。

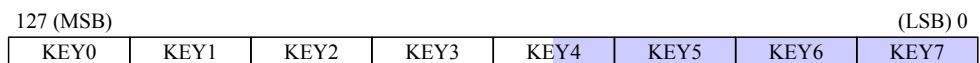

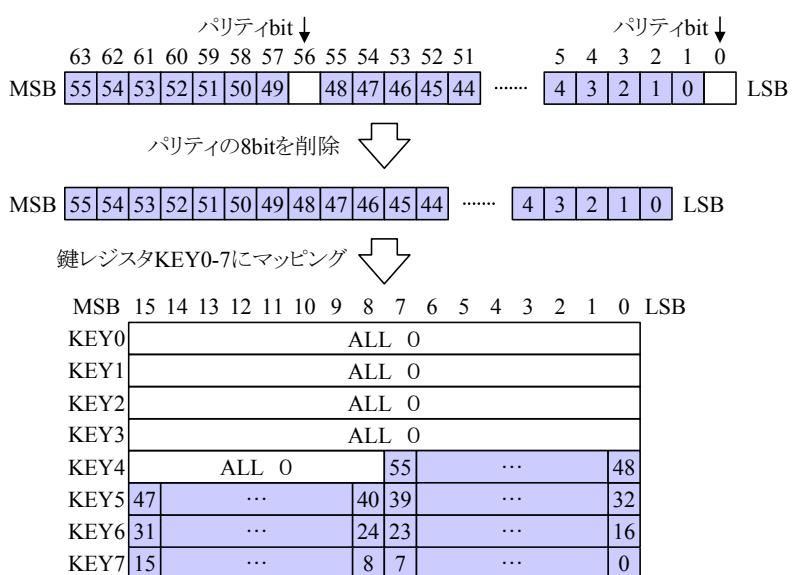

### ● 共通鍵暗号用鍵レジスタ:KEY0~7

鍵レジスタ KEY0~7 は、 $16\text{bit} \times 8 = 128\text{bit}$  分用意されているが、輸出規制の関係から KEY4 の下位 8bit と、KEY5~7 の合計 56bit 分だけを使用する。各暗号コアの鍵の取り扱いは次の通り。

DES: パリティビットを除いた 56bit の鍵を KEY4 の下位 8bit 及び KEY5~7 に入力する。DES 暗号コアはこの 56bit の鍵に対して回路中で、パリティビットを附加して 64 ビットとしている。

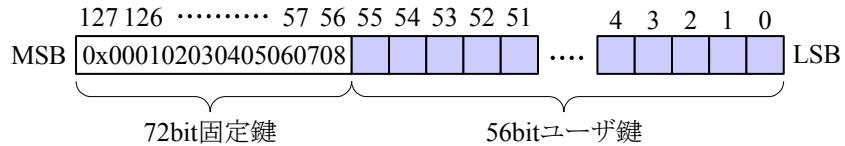

TDES: パリティビットを除いた 56bit の鍵を KEY4 の下位 8bit 及び KEY5~7 に入力する。T-DES 暗号コアには、鍵は以下のように入力される。

[191:64] : 0x000102030405060708090a0b0c0d0e0f (固定値)

[63:0] : ユーザが入力した 56bit の鍵にパリティを追加したもの

その他: アルゴリズムの鍵長が 128bit であるため、上位 72 ビットを以下のように固定し、KEY4 の下位 8bit 及び KEY5~7 の 56 ビットをユーザが設定する。

[127:56] : 0x000102030405060708

[55:0] : ユーザが入力した鍵

### ● GCM モード用 IV レジスタ:IV0~7

AES5 がサポートする GCM モードで使用する 128bit のイニシャルベクタ IV をセットする。

### ● 共通鍵暗号用入力テキストレジスタ:ITEXT0~31

入力テキストレジスタは、IP 選択レジスタ:IPSEL で指定される IP が使用する入力テキストを保持する。各暗号コアにより以下のようにデータサイズ、使用する入力テキストレジスタの場所が異なるので注意が必要である。

AES5(AES\_CTR\_PIPE): 128bit×4 ブロック分入力する。

ITEXT0~7 128bit 1 ブロック目入力

ITEXT8~15 128bit 2 ブロック目入力

ITEXT16~23 128bit 3 ブロック目入力

|                                           |           |           |         |         |         |         |         |

|-------------------------------------------|-----------|-----------|---------|---------|---------|---------|---------|

| ITEXT24~31                                | 128bit    | 4 ブロック目入力 |         |         |         |         |         |

| 64bit ブロック暗号群(MISTY1, TDES, DES, CAST128) |           |           |         |         |         |         |         |

| ITEXT0~3                                  | 64bit 入力  |           |         |         |         |         |         |

| ITEXT4~31                                 | 未使用       |           |         |         |         |         |         |

| 128bit ブロック暗号群                            |           |           |         |         |         |         |         |

| ITEXT0~7                                  | 128bit 入力 |           |         |         |         |         |         |

| ITEXT8~31                                 | 未使用       |           |         |         |         |         |         |

| 127 (MSB)                                 |           |           |         |         |         |         |         |

| ITEXT0                                    | ITEXT1    | ITEXT2    | ITEXT3  | ITEXT4  | ITEXT5  | ITEXT6  | ITEXT7  |

| ITEXT8                                    | ITEXT9    | ITEXT10   | ITEXT11 | ITEXT12 | ITEXT13 | ITEXT14 | ITEXT15 |

| ITEXT16                                   | ITEXT17   | ITEXT18   | ITEXT19 | ITEXT20 | ITEXT21 | ITEXT22 | ITEXT23 |

| ITEXT24                                   | ITEXT25   | ITEXT26   | ITEXT27 | ITEXT28 | ITEXT29 | ITEXT30 | ITEXT31 |

| (LSB) 0                                   |           |           |         |         |         |         |         |

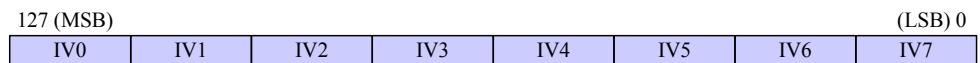

- 乱数レジスタ: **RAND0~7**

サイドチャネル攻撃対策を施した暗号コア AES8, AES9, AES10 において使用される乱数の SEED をセットする。1 度乱数レジスタに SEED が入力されると、暗号化処理の度にレジスタは新たな乱数で自動的に更新される。AES9 の乱数は、32bit であるため、SEED は上位側 RAND0~1 に詰めて入力する。

|       |       |       |       |       |       |       |       |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RAND0 | RAND1 | RAND2 | RAND3 | RAND4 | RAND5 | RAND6 | RAND7 |

|-------|-------|-------|-------|-------|-------|-------|-------|

- 共通鍵暗号用出力テキストレジスタ: **OTEXT0~31**

出力テキストレジスタは、出力選択レジスタ OUTSEL で選択されている IP の出力テキストを保持する。各暗号コアにより以下のように出力データサイズ、出力先のレジスタが異なるので注意が必要である。

また AES5 の仕様は他の暗号コアと異なり、入出力とも連続データした 128bit×4 ブロック単位で処理が行われる。IV レジスタにデータを入力すると、CTR モードの乱数生成部分の処理だけが行われ、出力テキストレジスタ OTEXT へはデータは出力されない。それに続いて入力テキストレジスタ ITEXT へデータがセットされると、暗号化処理(前回生成した乱数と入力テキストとの XOR)が行われて OUTTEXT へデータが出力されるとともに、次の入力テキストに対して使用される乱数生成が行われる。

AES5(AES\_CTR\_PIPE): 128bit×4 ブロック分出力される。

|            |        |           |

|------------|--------|-----------|

| OTEXT0~7   | 128bit | 1 ブロック目入力 |

| OTEXT8~15  | 128bit | 2 ブロック目入力 |

| OTEXT16~23 | 128bit | 3 ブロック目入力 |

| OTEXT24~31 | 128bit | 4 ブロック目入力 |

64bit ブロック暗号群(MISTY1, TDES, DES, CAST128)

|          |                    |

|----------|--------------------|

| OTXT0~3  | 64bit 出力           |

| OTEXT4~7 | 0x0000000000000000 |

| OTXT8~31 | 未使用                |

128bit ブロック暗号群

|           |           |

|-----------|-----------|

| OTEXT0~7  | 128bit 出力 |

| OTEXT8~31 | 未使用       |

| 127 (MSB) (LSB) 0 |         |         |         |         |         |         |         |

|-------------------|---------|---------|---------|---------|---------|---------|---------|

| OTEXT0            | OTEXT1  | OTEXT2  | OTEXT3  | OTEXT4  | OTEXT5  | OTEXT6  | OTEXT7  |

| OTEXT8            | OTEXT9  | OTEXT10 | OTEXT11 | OTEXT12 | OTEXT13 | OTEXT14 | OTEXT15 |

| OTEXT16           | OTEXT17 | OTEXT18 | OTEXT19 | OTEXT20 | OTEXT21 | OTEXT22 | OTEXT23 |

| OTEXT24           | OTEXT25 | OTEXT26 | OTEXT27 | OTEXT28 | OTEXT29 | OTEXT30 | OTEXT31 |

### ● 共通鍵暗号用中間値レジスタ:RDATA0~7

AES6 実行時の各ラウンドの中間値の読み出しのためのレジスタ群で、IP 選択レジスタ IPSEL/OUTSEL で AES6 が選ばれ、かつ、ラウンド選択レジスタ RSEL の DEN ビットを'1'にした場合に有効となる。中間値の保持は以下の 2 つのケースについて実行される。なお、中間値出力機能の使用時でも暗号化・復号処理は最後まで継続し、その最終結果が出力テキストレジスタ OTEXT に保持される。

#### 1. 中間値を保持するラウンドを指定する場合

ラウンド選択レジスタ: RSEL[DRSEL] で示されるラウンドの中間値が保持され、データの並びは RDATA0 に最上位 16 ビット分のデータ、以下 RDATA1, RDATA2... と続く。

#### 2. Fault Error 発生時

ラウンド処理中、途中結果に Fault Error が発生した際には(AES6 のモジュール AES\_FA でエラー検出信号が Err[0]=1 にアサートされる)、ラウンド選択レジスタ RSEL の DERR がアサートされると共に、そのときの中間値が保持される。

| 127 (MSB) (LSB) 0 |        |        |        |        |        |        |        |

|-------------------|--------|--------|--------|--------|--------|--------|--------|

| RDATA0            | RDATA1 | RDATA2 | RSATA3 | RDATA4 | RDATA5 | RDATA6 | RDATA7 |

### ● 共通鍵暗号用中間鍵レジスタ:RKEY0~7

AES6 実行時の各ラウンドの中間鍵の読み出しのためのレジスタ群で、IP 選択レジスタ IPSEL/OUTSEL で AES6 が選ばれ、かつ、ラウンド選択レジスタ RSEL の KEN ビットを'1'にした場合に有効となる。中間鍵の保持は以下の 2 つのケースについて実行される。なお、中間鍵出力機能の使用時でも暗号化・復号処理は最後まで継続し、その最終結果が出力テキストレジスタ OTEXT に保持される。

#### 1. 中間鍵を保持するラウンドを指定する場合

ラウンド選択レジスタ: RSEL[KRSEL] で示されるラウンドの中間鍵が保持され、データの並びは RKEY0 に最上位 16 ビット分のデータ、以下 RKEY1, RKEY2... と続く。

#### 2. Fault Error 発生時

ラウンド処理中、途中結果に Fault Error が発生した際には(AES6 のモジュール AES\_FA でエラー検出信号が Err[0]=1 にアサートされる)、ラウンド選択レジスタ RSEL の DERR がアサートされると共に、そのときの中間鍵が保持される。中間鍵にエラーがあつても、それは全ラウンドの処理が終了するまで判定することができない(AES\_FA でエラー検出信号が Err[1]=1 にアサートされるのは最終ラウンド終了時に限られる)。したがって KERR はラウンド処理途中でアサートされることではなく、最終ラウンド処理後となる。このため中間鍵レジスタは、“途中結果”にエラーが生じたときの中間鍵を保存する目的に使用される。逆に、中間鍵にエラーがあつてもどのラウンドかは分からいため、エラー発生時の途中結果は保存されれない。

| 127 (MSB) (LSB) 0 |       |       |       |       |       |       |       |

|-------------------|-------|-------|-------|-------|-------|-------|-------|

| RKEY0             | RKEY1 | RKEY2 | RKEY3 | RKEY4 | RKEY5 | RKEY6 | RKEY7 |

- 公開鍵暗号用指数レジスタ:EXP0~31

RSA の 512 ビットの指数を入力する. EXP0 に最上位 16 ビット分の指数が保持され, 以下 EXP1, EXP2, ...と続く. ECC では使用しない.

- 公開鍵暗号用法レジスタ:MOD0~31

RSA の 512 ビットの法を入力する. MOD0 に最上位 16 ビット分の法が保持され, 以下 MOD1, MOD2, ...と続く. ECC では使用しない.

- 公開鍵暗号用前処理演算結果レジスタ:PREDAT0~15

RSA の CTR 処理時の 256 ビットの前処理演算結果を入力する. PREDAT0 に最上位 16 ビット分の指数が保持され, 以下 PREDAT1, PREDAT2, ...と続く. ECC では使用しない.

- 公開鍵暗号用入力データレジスタ:IDATA0~31

RSA では 512 ビットのデータ入力に使用され, IDATAP0 に最上位 16 ビット分の入力データが保持され, 以下 IDATA1, IDATA2, ...と続く.

ECC では下記のデータを入力する.

IDATA0~3:64bit 秘密鍵データ

IDATA4~7: サイドチャネル対策用 64bit 乱数データ.

将来サポート予定であり, 今回の ECC コアでは使用されない.

IDATA8~11: 入力点の Affine 座標における x 座標データ(64bit)

IDATA12~15: 入力点の射影座標における z 座標データ(64bit)

IDATA16~19: 楕円曲線パラメータ b(64it)

IDATA20~31: 未使用

いずれも, 添字が若い側に上位のデータを入力する.

- 公開鍵暗号用出力データレジスタ:ODATA0~31

RSA では 512 ビットの計算結果が出力される. ODATA0 に最上位 16 ビットの計算結果が保持され, 以下 ODATA1, ODATA2, ...と続く.

ECC では ODATA0~3 に 64 ビットの計算結果が出力される. ODATA0 に最上位の計算結果が保持され, 以下 ODATA1, ODATA2, ODATA3 と続く. ODATA4~31 は未使用である.

- バージョンレジスタ:VER

暗号 LSI のバージョンを表す読み出し専用レジスタ. 130nm 版は固定値 0x0450A, 90nm 版は固定値 0x34F9 が読み出される.

### 3.4 クロックツリー

暗号 LSI では、インターフェースレジスタの設定により、測定対象とするコアだけに動作クロックを供給する。一方、故障解析を容易に行なうため、インターフェース回路クロックとコアクロックとを分離し、コアクロックにのみノイズを印加できる構成としている。

図 3.5 クロック系統図

### 3.5 リセット

図 3.6 は評価用 LSI のリセット系統であり、リセットシーケンスは以下の通りである。なお、IP 選択レジスタで選択されていない暗号 IP コアにはクロックが供給されず、リセット信号がアサートされたままであることに注意が必要である。

#### ① HRST\_N アサート/デアサート

HRST\_N 信号をアサートすることにより、インターフェース回路のコントロールレジスタ CONT 内 IPRST ビットは 1 にセットされ、各 IP のリセット信号がすべてアサートされる。その後、HRST\_N 信号をデアサートする。この状態が暗号 LSI の初期状態である。

#### ② CLK\_A, CLK\_B 入力

インターフェース回路が動作可能な状態となる。この時点で、各暗号コアにクロックは供給されておらず、リセット信号もアサートされたままである。

#### ③ IP コア選択

インターフェース回路の IP 選択レジスタ IPSEL 中の該当ビットをセットし、動作させる IP を選択する。IPSEL で選択されたコアに対してクロックが供給される。この時点では、選択されたコアを含め各 IP へのリセット信号はアサートされたままである。

#### ④ 選択したコアのリセット解除

インターフェース回路のコントロールレジスタ CONT 中の IPRST ビットに 0 を書き込むこと

で、③で選択したコアのリセット信号がデアサートされ、リセットが解除される。なおリセットシーケンスではないが、この後に出力選択レジスタ OUTSEL も設定しておく必要がある。

図 3.6 リセット系統

### 3.6 付帶機能

#### ● コアクロックとインターフェースクロック

故障解析を容易にすることを目的に、コアのみに動作クロック由来の故障を印加するため、コアクロック CLK\_A とインターフェースクロック CLK\_B を分離している。そして、暗号 LSI 内同期化回路は簡略化のため、CLK\_A と CLK\_B の位相差は  $180^\circ$ （反転クロック）であることを前提とする設計を行なっている。

### ● 鍵長制限

暗号 LSI は輸出管理対象とならないよう、共通鍵アルゴリズムの鍵長は 56 ビットに、RSA と ECC は 512 ビットと 64 ビットに制限されている。

DES はパリティビットを含まない 56 ビットの鍵を KEY4 の下位 8bit 及び KEY5~7 に入力する。DES の鍵データと暗号 LSI との対応を図 3.6 に示す。T-DES の上位[191:64]は以下の固定値がコアに供給される。下位[63:0]の扱いは DES と同じである。

[191:64] 0x000102030405060708090a0b0c0d0e0f (固定值)

図 3.7 DES コア鍵データビットアサイン

その他共通鍵暗号アルゴリズムズムの鍵長は128ビットであるため、図3.8に示したように上位72ビットを固定値とし、下位56ビットだけをユーザが設定できるようにしている。

[127:56] 0x000102030405060708 (固定値)

[55:0] 入力された鍵 KEY4 下位8ビットとKEY5-7を併せた56ビット

図3.8 共通鍵データビットアサイン

### ● 遅延実行

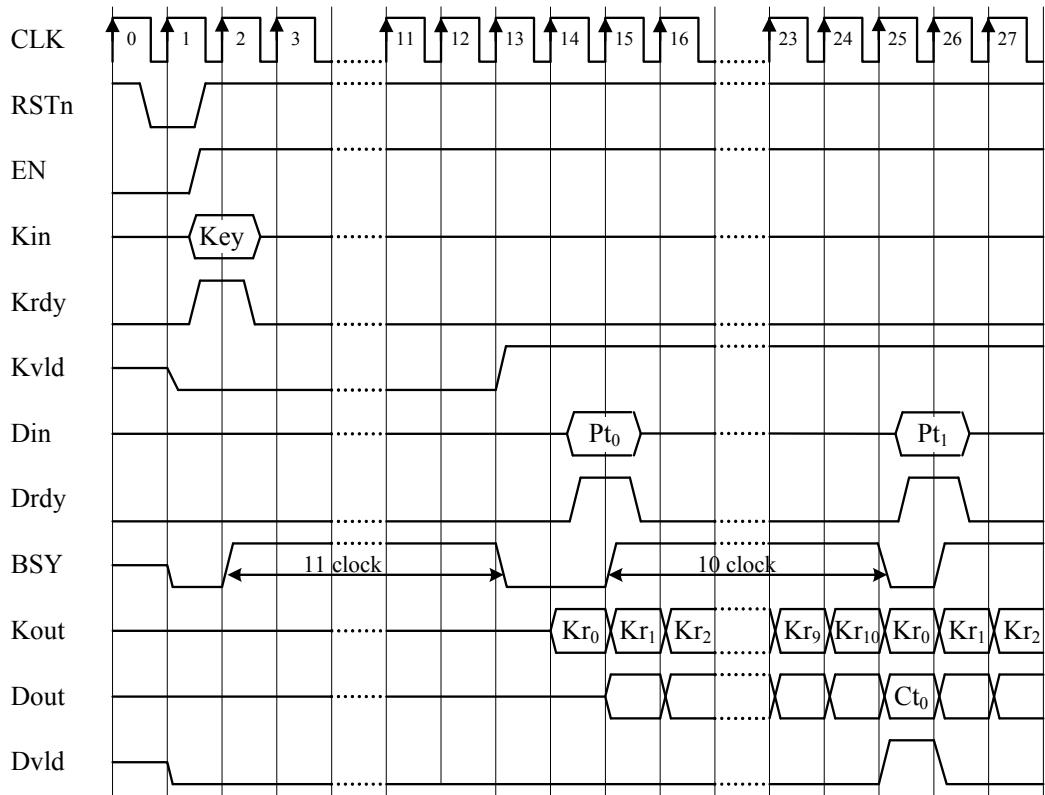

暗号LSIの暗号処理中の電力波形を精度よく観測できるように、鍵設定やデータ入出力と暗号処理の時間をずらしている。具体的には、コントロールレジスタCONTのRUNビットを設定して、処理開始を指示してから8CLK後に処理開始要求信号START\_Nがアサートされ、さらにその8CLK後に暗号アルゴリズムコアが処理を開始して処理中であることを示すEXECがHighとなる。アルゴリズムコアの処理終了によりEXECがLowに落ちると、その8CLK後に処理完了を示すEND\_Nがアサートされる。更にその8CLK後にコントロールレジスタCONT[RUN]が0となる。これら一連の動作の詳細を図3.9に示す。なお、CLKはいずれもCLK\_A換算である。

図3.9 遅延実行のタイミングチャート

### ● ノイズ発生源

対象とする暗号IP以外のIPをノイズ発生源として利用し、電力解析や電磁波解析に与える影響を評価することが可能である。具体的には、IP選択レジスタIPSELで複数の暗号IPを選択し、出力選択レジスタOUTSELで評価対象のIPだけを選択することで実現される。

### ● 評価用信号の出力抑止機能

電力波形や電磁波形測定時に制御回路のノイズ放射を低減するため、評価信号START\_N, END\_N, EXEC, STATEの出力を抑止する次の2つの機能を設けている。

- モードレジスタ MODE[OUTINH]を“10”に設定することで、全ての評価用信号出力を0にする。

2. MODE[OUTINH]を”11”に設定することで、START\_N 以外の評価信号出力を 0 にする。

- **自走モード**

AES0 では、コントロールレジスタ CONT[RUN]を 1 にすることで、0.3 秒ごとに自動的に暗号化または復号処理を繰り返す自走モードでの動作が可能である。1 回目の処理が終了すると、コントロールレジスタ CONT[RUN]は 0 にリセットされ、そのまま 2 回目以降の処理が続行される。出力抑止機能を使用していない限り、START\_N, EXEC, END\_N は上記の遅延実行に応じて制御される。自走モードに入ると他の処理は実行できなくなり、自走モードの解除には、電源リセットもしくは HRST\_N をアサートする必要がある。なお、入力テキストは次の 2 つパターンから選択できる。

1. モードレジスタ MODE[FRUN]を “10” に設定することで、入力テキストレジスタ ITEXT にセットした平文または暗号文を初期値をとして、暗号化または復号処理が終わるごとに、自動的に+1 インクリメントを行う。

2. モードレジスタ MODE[FRUN]を “11” に設定することで、暗号化または復号処理完了時の暗号文または平文を、次の処理の入力とする。なお入力の初期値は、テキストレジスタ ITEXT にセットした平文または暗号文である。

- **入力テキストレジスタ ITEXT の取り扱い**

共通鍵暗号では以下に示すように、IP 毎に入力データサイズと入力テキストレジスタのマッピングが異なっているので注意が必要である。

1. AES5 (CTR モード+4 段パイプライン実装)

|            |                     |

|------------|---------------------|

| ITEXT0~7   | 128bit 入力 (1 ブロック目) |

| ITEXT8~15  | 128bit 入力 (2 ブロック目) |

| ITEXT16~23 | 128bit 入力 (3 ブロック目) |

| ITEXT24~31 | 128bit 入力 (4 ブロック目) |

2. その他の 128 bit ブロック暗号

|           |           |

|-----------|-----------|

| ITEXT0~7  | 128bit 入力 |

| ITEXT8~31 | 未使用       |

3. 64bit ブロック暗号

|           |          |

|-----------|----------|

| ITEXT0~3  | 64bit 入力 |

| ITEXT4~31 | 未使用      |

- **出力テキストレジスタ OTEXT の取り扱い**

共通鍵暗号では以下に示すように、IP 每に出力データサイズと出力テキストレジスタのマッピングが異なっているので注意が必要である。

1. AES5 (CTR モード+4 段パイプライン実装)

|            |                     |

|------------|---------------------|

| OTEXT0~7   | 128bit 出力 (1 ブロック目) |

| OTEXT8~15  | 128bit 出力 (2 ブロック目) |

| OTEXT16~23 | 128bit 出力 (3 ブロック目) |

| OTEXT24~31 | 128bit 出力 (4 ブロック目) |

2. その他の 128 bit ブロック暗号

|           |            |

|-----------|------------|

| OTEXT0~7  | 128bit 出力  |

| OTEXT8~31 | don't care |

3. 64bit ブロック暗号

|           |                    |

|-----------|--------------------|

| OTEXT0~3  | 64bit 出力           |

| OTEXT4~7  | 0x0000000000000000 |

| OTEXT8~31 | don't care         |

### ● DPA 対策用の乱数レジスタ RAND の取り扱い

AES8(Masked AND Operation)、AES9(MDPL)、AES10(Threshold Implementation)で使用する初期乱数のシードを、乱数レジスタ RAND0~7 に入力するが、AES9 では乱数シードは 32bit なのでレジスタの上位側が RAND0~1 だけが有効となる。

### ● AES5(CTR モードサポートパイプライン)の CTR 動作について

他の暗号コアと異なり、データ入出力は 128bit×4 ブロック連続して行われる。IV レジスタにカウンタの初期値を入力した直後には、CTR モード 4 ブロック分の乱数生成が行われるが、入力テキストレジスタ ITEXT に平文(または暗号文)が 4 ブロック入力されるまでは出力テキストレジスタ OTEXT からの出力はない。4 ブロックの暗号文(または平文)が出力されると、次の 4 ブロックの乱数生成が行われる。

### ● 中間値の出力

AES6(故障利用解析攻撃対策版)は中間値の出力が可能である。IP 選択レジスタ IPSEL0 および出力選択レジスタ OUTSEL0 で AES6 が選択され、かつラウンド選択レジスタ RSEL[DEN]が 1 の時に中間値レジスタ RDATA0~7 に中間値が出力される。なお、出力される中間値のラウンドは、ラウンド選択レジスタ RSEL[DRSEL]で決定する。

### ● 中間鍵の出力

AES6 は中間鍵(ラウンド鍵)の出力が可能である。IP 選択レジスタ IPSEL0 および出力選択レジスタ OUTSEL0 で AES6 が選択され、かつラウンド選択レジスタ RSEL[KEN]が 1 の時に中間鍵レジスタ RKEY0~7 に中間鍵が出力される。なお、出力されるラウンド鍵はラウンド選択レジスタ RSEL[KRSEL]で決定する。

### ● 故障利用解析攻撃(FA: Fault injection Attack)への対応

AES6において、演算中に Fault Error が起きると、ラウンド選択レジスタの RSEL[KERR]あるいは RSEL[DERR]が 1 となり、その時の中間値とラウンド鍵がそれぞれ中間値レジスタ RDATA0~7 および中間鍵レジスタ RKEY0~7 に出力される。

## 4 LSI の物理レイアウト

### 4.1 130nm バージョン

130nm スタンダードセルライブラリを用いた暗号 LSI の論理合成後のレイアウト情報について述べる。表 4.1 は LSI の概要で、 $5 \times 5 \text{ mm}^2$  のダイサイズのうち、24.95% のゲートが使用されている。目標の動作周波数は 24MHz (41ns cycle) であるが、レイアウト時のタイミング修正を容易にするため、30% のマージンを加え 31MHz で論理合成を行った。また多くの Setup マージンを確保するため、入出力にも大きな遅延を与えていている。

表 4.1 暗号 LSI の概要

| 項目       |                                                       |

|----------|-------------------------------------------------------|

| テクノロジ    | 0.13um Logic General Purpose<br>1P8M 1.2V-3.3V CU FSG |

| ウェハプロセス  | TSMC CLN130G<br>130nm CMOS, アルミ 7 層配線                 |

| コア電源電圧   | $1.2 \pm 0.12\text{V}$                                |

| I/O 電源電圧 | $3.3 \pm 0.16\text{V}$                                |

| 動作周波数    | 24MHz (41ns)                                          |

| データエリア   | $5 \times 5 \text{ mm}^2$                             |

| セル使用数    | 4,129,178/16,550,023<br>(セル面積/セル配置可能面積)               |

| セル使用率    | 24.95%                                                |

| PAD 数    | 160 個                                                 |

| カスタムセル   | SRAM                                                  |

表 4.2 使用 EDA Tool

| 用途       | ソフト名            | ベンダー     | バージョン          |

|----------|-----------------|----------|----------------|

| 論理合成     | Design Compiler | Synopsys | Z-2007.03-SP5  |

| 配置・配線    | SOC Encounter   | Cadence  | v06.20-s285_1  |

| RC 抽出    | Star-RCXT       | Synopsys | Z-2006.12-SP1  |

| クロストーク抽出 | CeltIC          | Cadence  | v06.20-s075_1  |

| STA      | PrimeTimeSI     | Synopsys | Z-2007.06.-SP3 |

| レイアウト検証  | Calibre         | Mentor   | v2008.3-25.16  |

| Power 検証 | AstroRail       | Synopsys | Z-2007.03-SP8  |

| 等価検証     | Formality       | Synopsys | Z-2007.06.SP-3 |

表 4.3 使用ライブラリ

| 分類            | ライブラリ                                            | バージョン    |

|---------------|--------------------------------------------------|----------|

| Standard Cell | SAGE-X Standard Cells<br>(TSMC CL013G)FB         | 2007q1v2 |

|               | SAGE-X Standard Cells<br>(TSMC CL013G) FX-CeltIC | 2005q3v1 |

| Digital I/O   | EZBond, I/O, TPZ013G3, 1.2V/3.3V                 | 210c     |

| RAM           | 2P-RF ADV(TSMC CL013G) FB                        | 2004q2v1 |

|               | SP-RF ADV(TSMC CL013G) FB                        | 2003q4v1 |

表 4.4 論理合成条件

| 条件項目   | 条件値                        |

|--------|----------------------------|

| 動作周波数  | 31MHz (32ns) 24MHz+30%マージン |

| 入力遅延   | 2ns                        |

| 出力遅延   | 2ns                        |

| 外部負荷容量 | 20pf                       |

| 仮想配線遅延 | tsmc130_w110               |

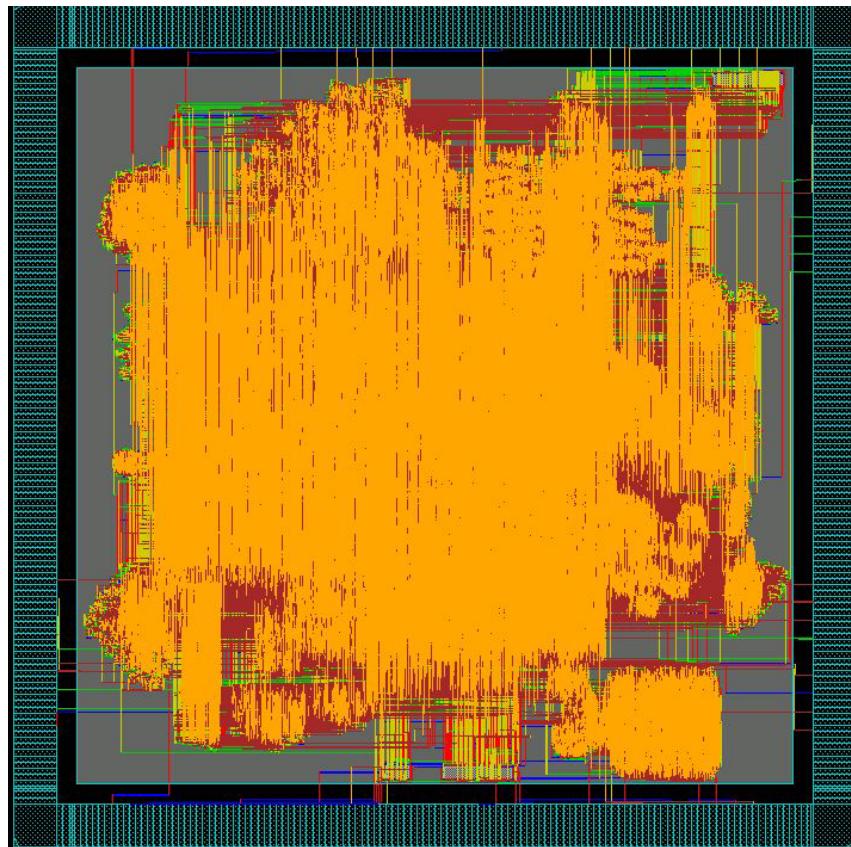

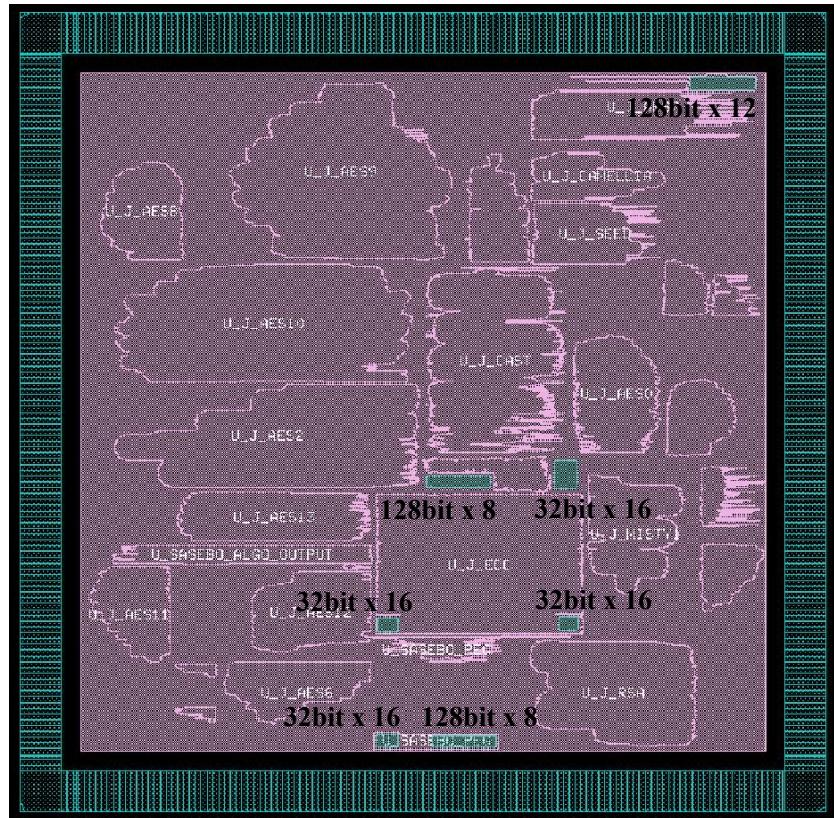

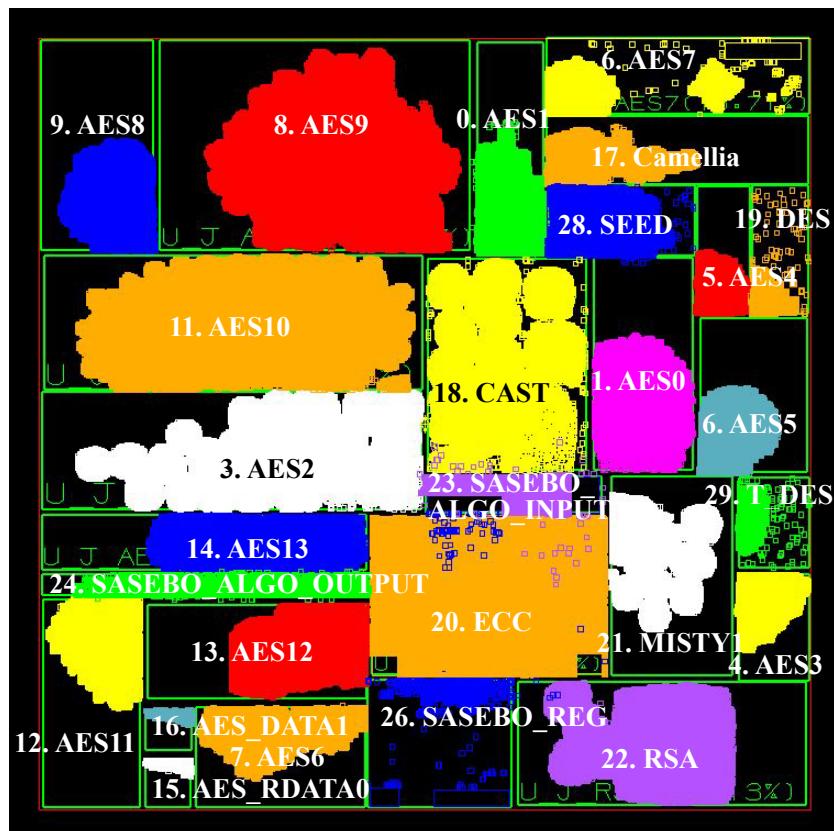

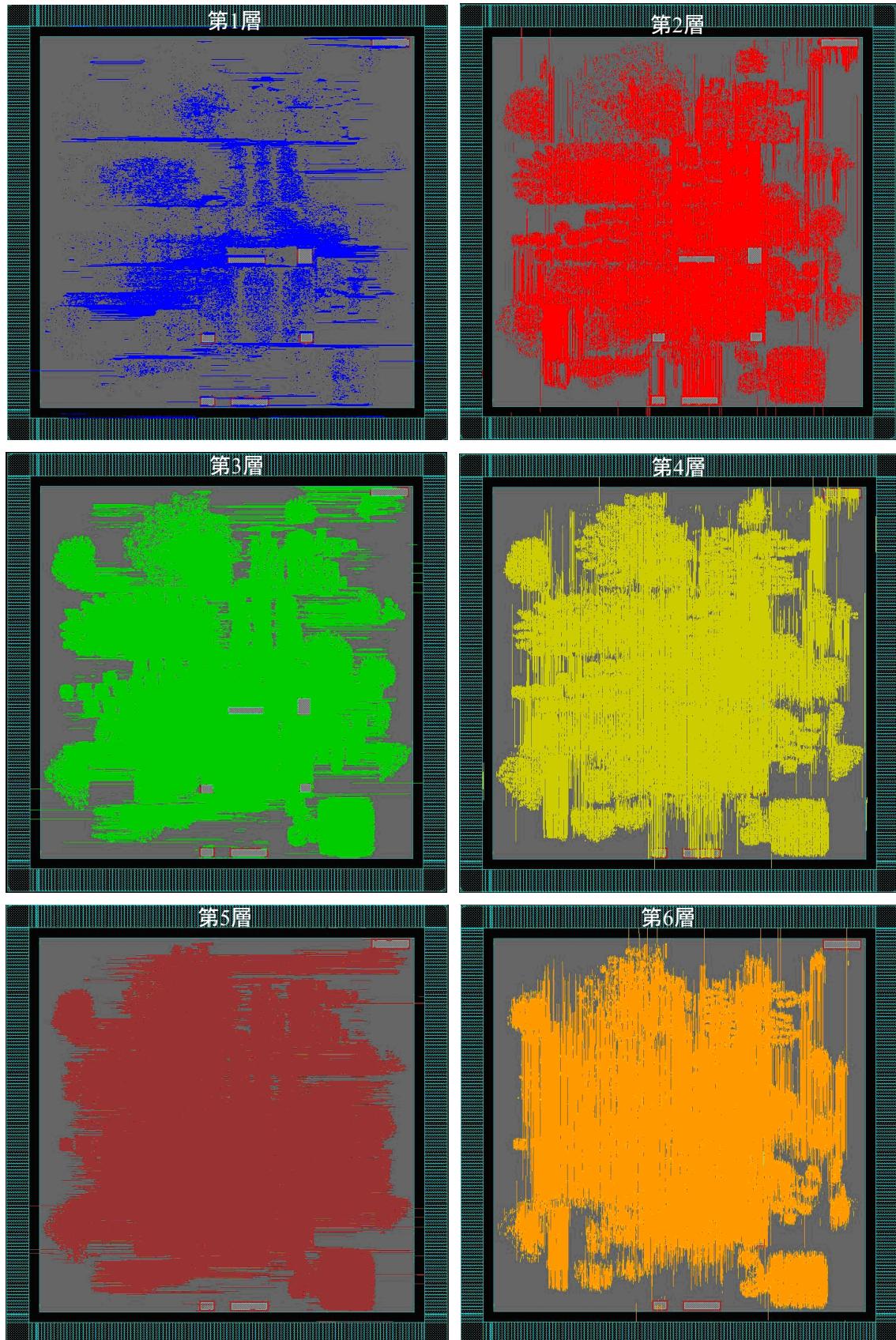

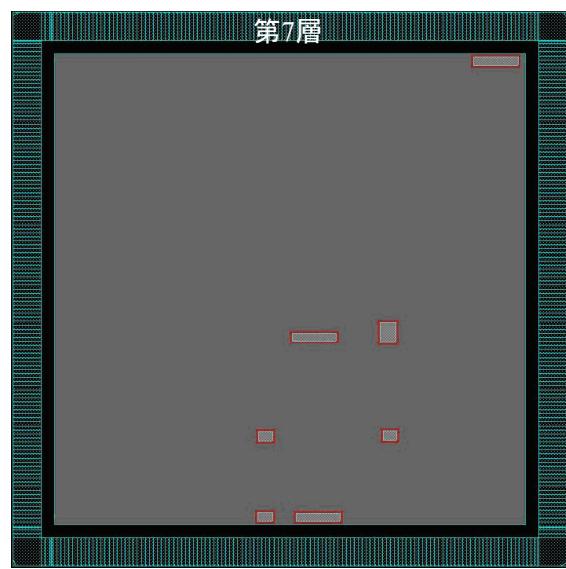

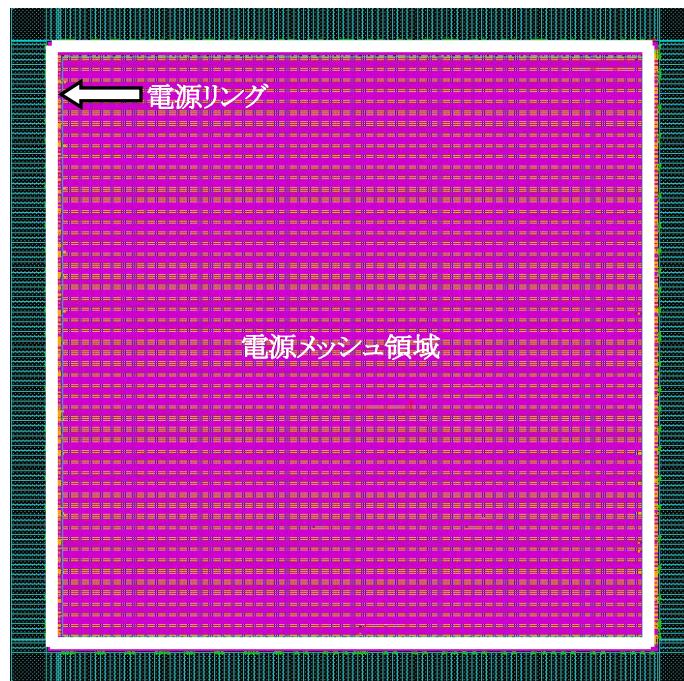

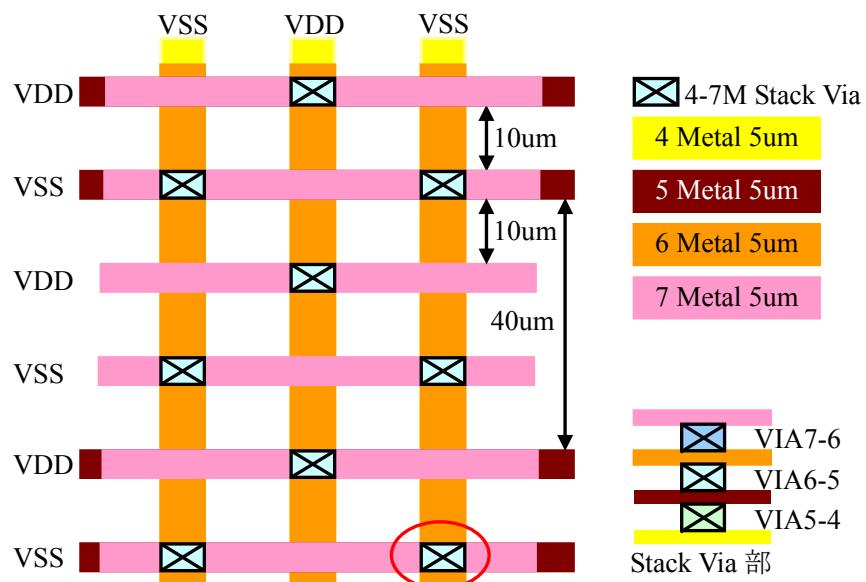

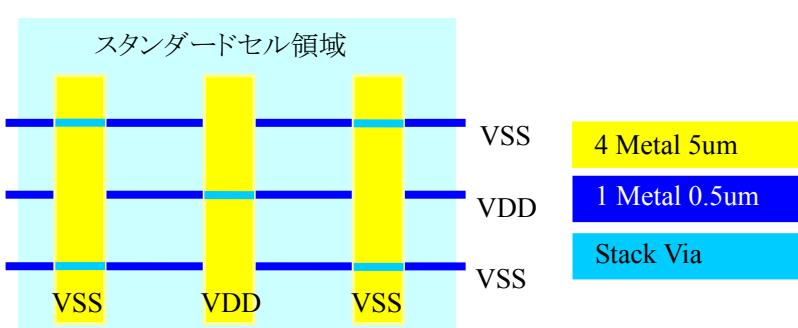

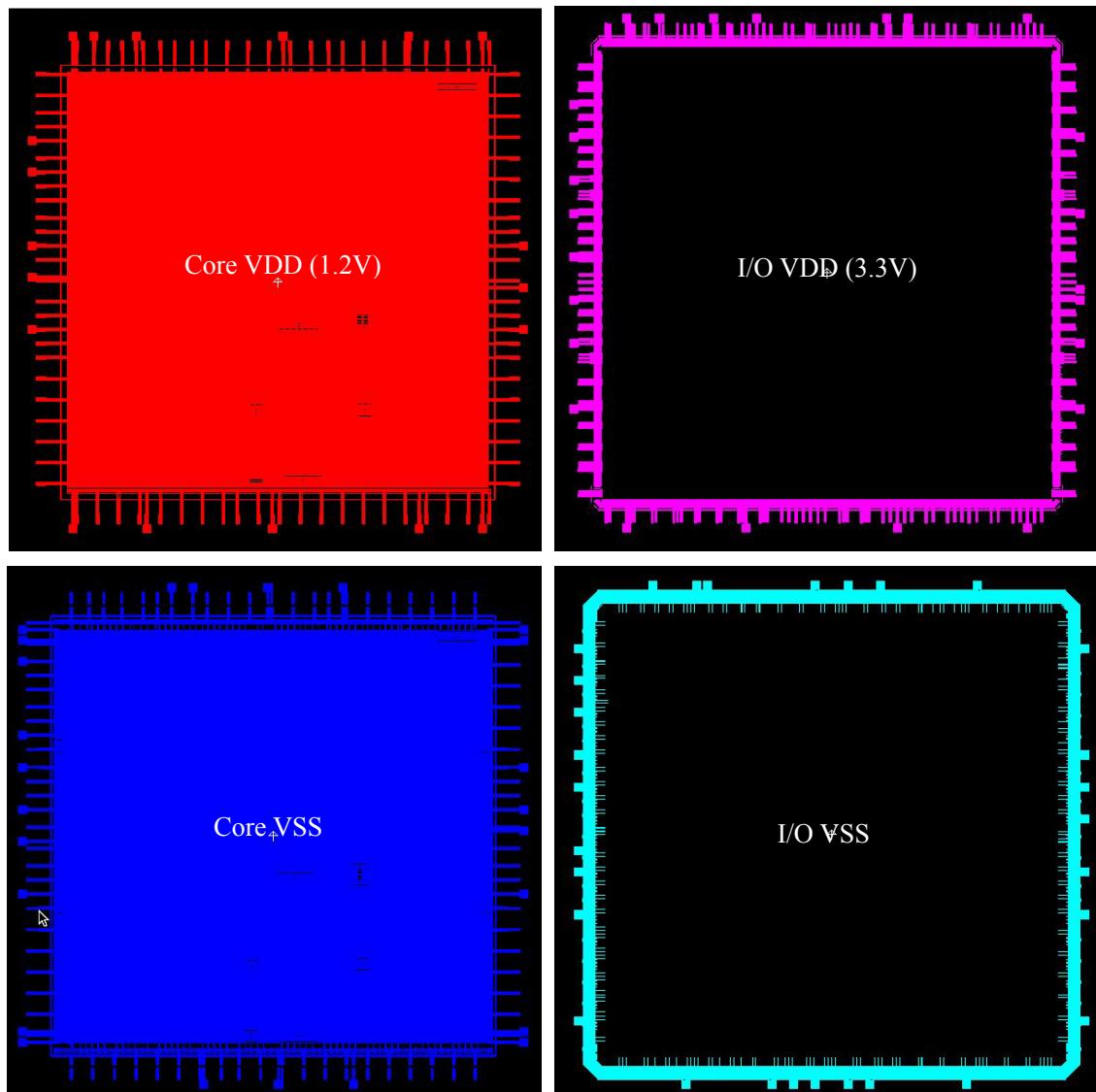

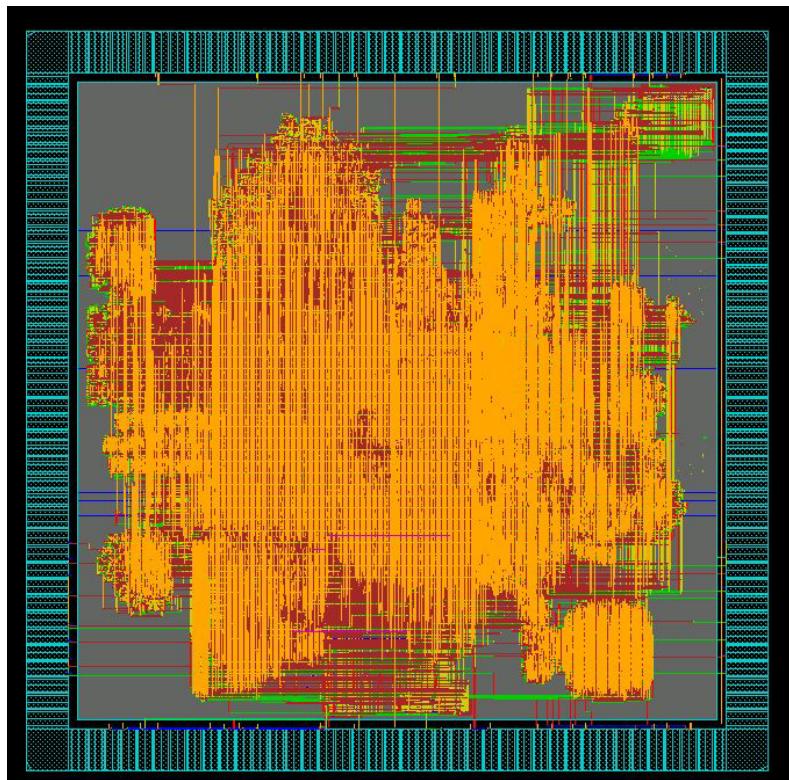

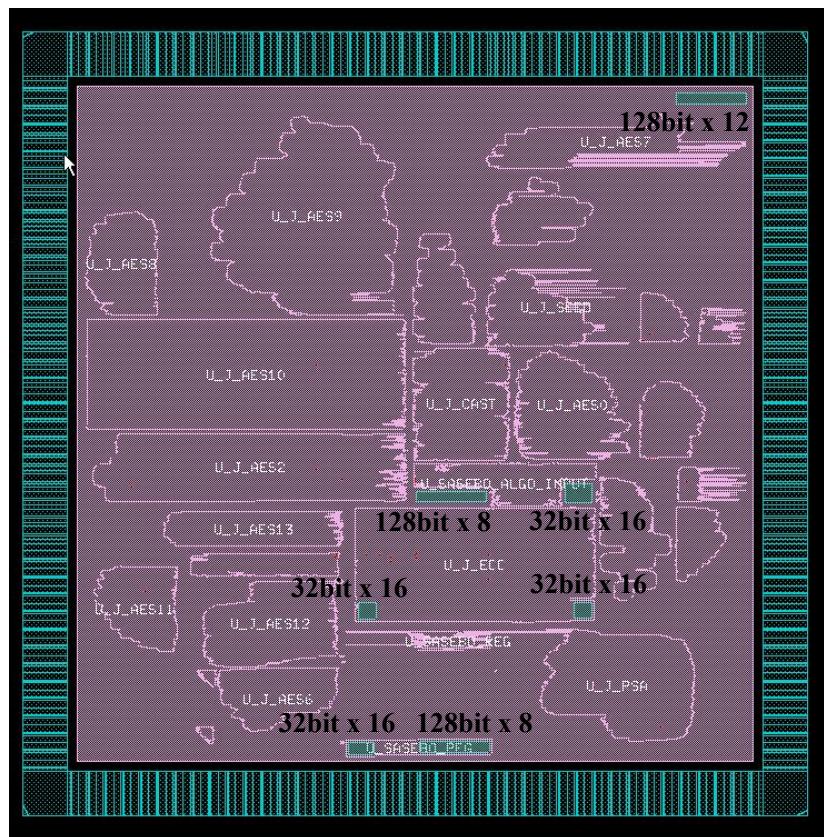

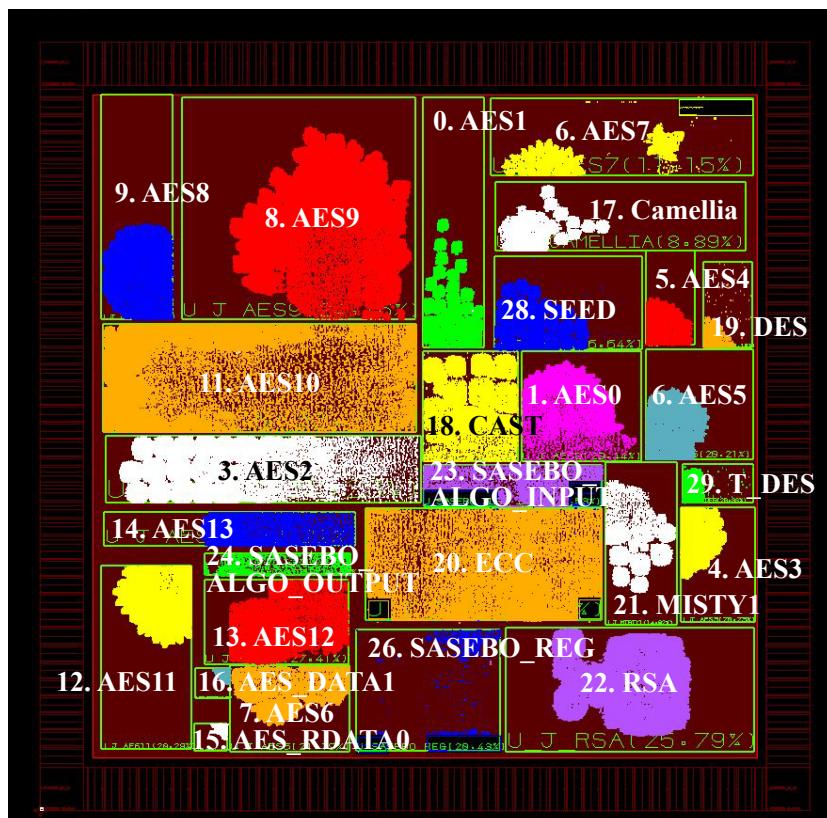

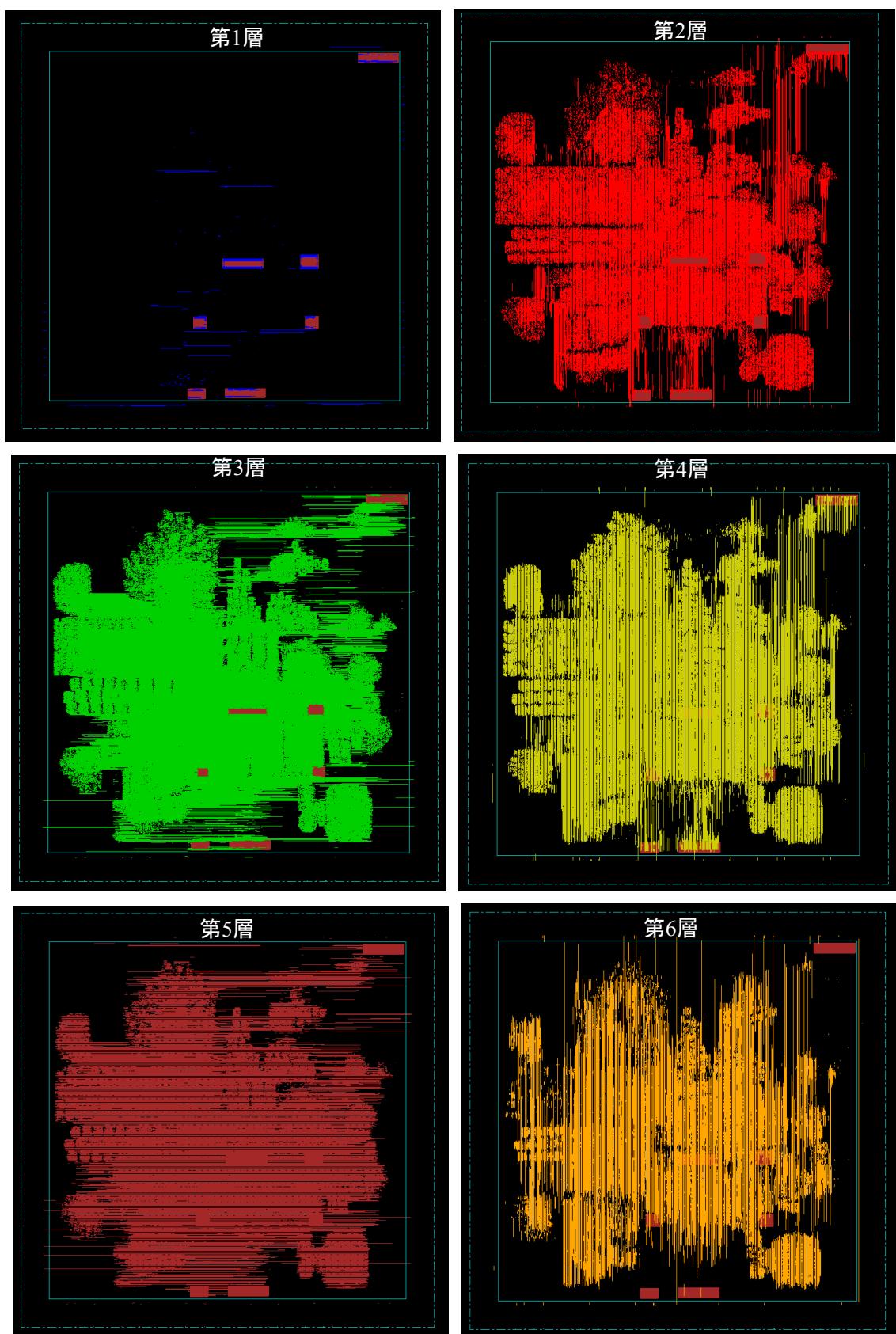

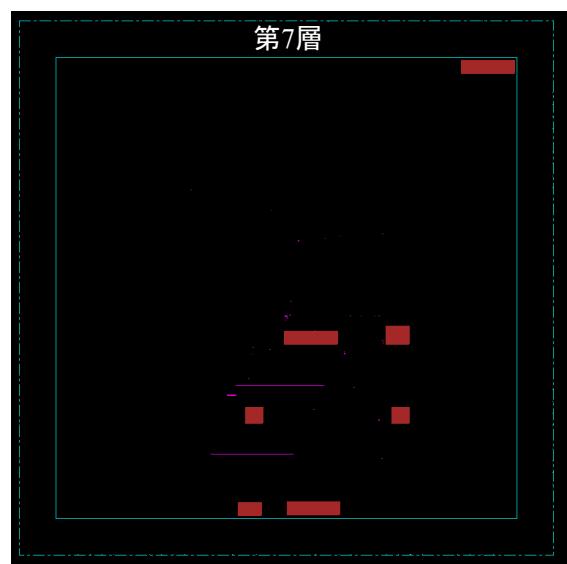

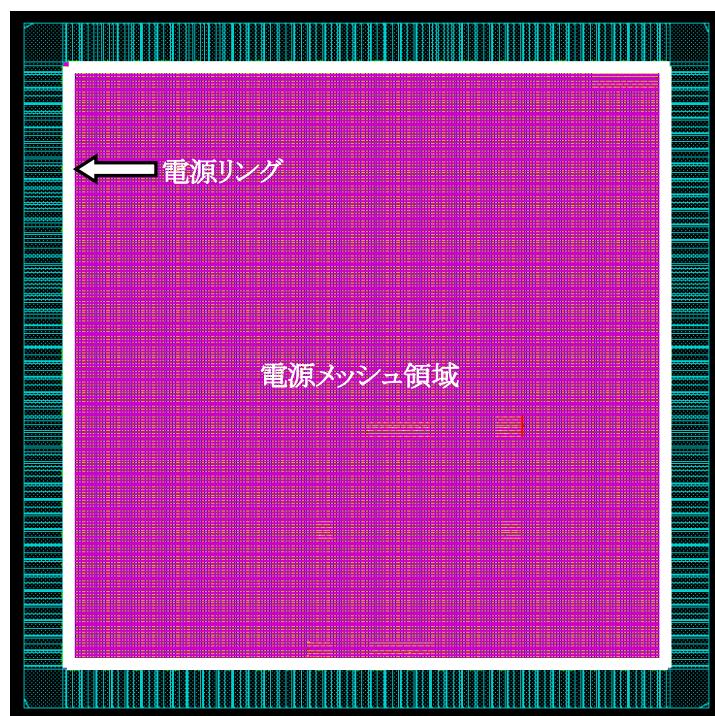

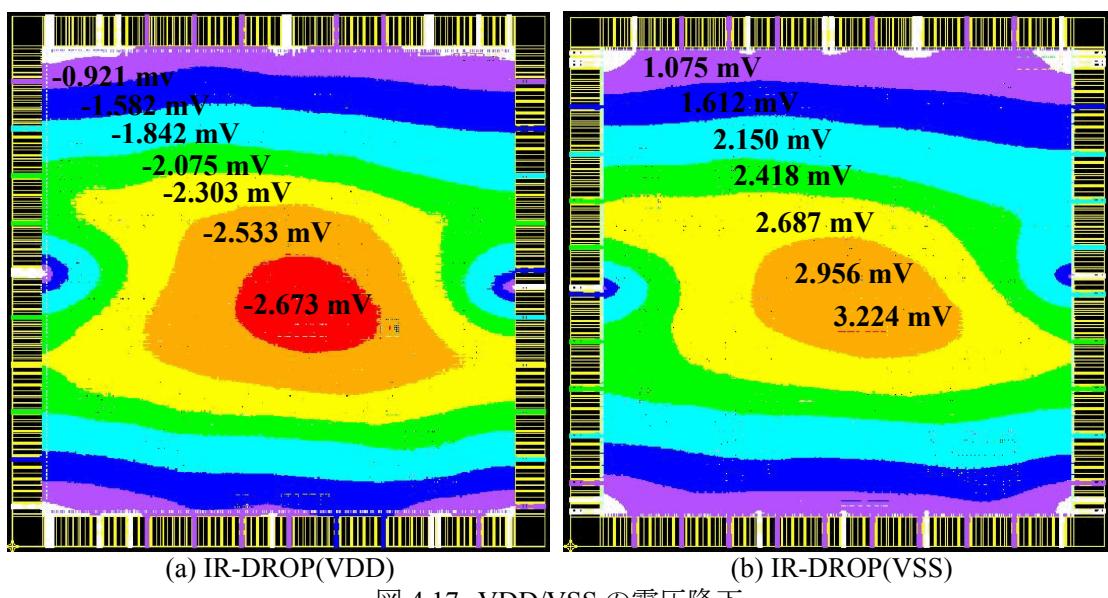

図 4.1 は暗号 LSI の電源ラインを除いた Top View を、図 4.2 はレジスタアレイの配置を、図 4.3 は各暗号モジュールの配置を示している。また、表 4.5 はそれらモジュールの回路規模の一覧である。また、表 2.11 は製造時のプロセスパラメータが Typical の場合において、動作環境が Worst (125°C 1.08V), Typical (25°C 1.20V), Best (-40°C 1.32V) のときの LSI の動作速度であり、表 4.6 は各暗号モジュールの性能を示している。最も遅いモジュールはサイドチャネル攻撃対策の MDPL (Masked Dual-rail Precharge Logic)を用いた AES 回路で、Worst 条件において動作周波数 25.78 MHz (Typical: 41.24MHz, Best: 62.68MHz) で、回路規模も最大の 124,319 ゲートであった。ターゲットの 24MHz を達成しているが、表 4.6 より LSI 全体では Worst 条件において 20.410MHz (Typical: 24.889MHz, Best: 29.410MHz) と 24MHz 動作が達成されなかった。しかしながら、本 LSI を実装する評価ボード SASEBO-R ではクロックを標準の 24MHz から変更可能であり、コア電圧も可変なため、実験において問題が生じることはない。

図 4.1 暗号 LSI の Top View

図 4.2 レジスタアレイ配置図

図4.3 暗号モジュール配置図

表 4.5 モジュール面積一覧

| モジュール名                       | 面積 ( $\mu\text{m}^2$ ) | 面積 (%) | ゲート数    |

|------------------------------|------------------------|--------|---------|

| 1. AES0 (合成体 S-box)          | 129,763                | 2.7    | 25,483  |

| 2. AES1 (テーブル S-box)         | 105,097                | 2.2    | 20,639  |

| 3. AES2 (1-stage PPRM S-box) | 314,702                | 6.5    | 61,801  |

| 4. AES3 (3-stage PPRM S-box) | 84,230                 | 1.7    | 16,541  |

| 5. AES4 (合成体 S-box)          | 61,408                 | 1.3    | 12,059  |

| 6. AES5 (CTR モード)            | 112,794                | 2.3    | 22,150  |

| 7. AES6 (FA 対策済)             | 105,125                | 2.2    | 20,644  |

| 8. AES7 (ラウンド鍵事前生成)          | 93,655                 | 1.9    | 18,392  |

| 9. AES8 (MAO)                | 179,253                | 3.7    | 35,202  |

| 10. AES9 (MDPL)              | 633,056                | 13.1   | 124,319 |

| 11. AES10 (Threshold)        | 555,510                | 11.5   | 109,090 |

| 12. AES11 (WDDL)             | 152,225                | 3.1    | 29,894  |

| 13. AES12 (疑似 RSL)           | 169,789                | 3.5    | 33,343  |

| 14. AES13 (疑似 RSL)           | 99,295                 | 2.1    | 19,499  |

| 15. AES_RDATA2               | 7,373                  | 0.2    | 1,448   |

| 16. AES_RDATA1               | 7,387                  | 0.2    | 1,451   |

| 17. Camellia                 | 73,407                 | 1.5    | 14,416  |

| 18. CAST                     | 148,921                | 3.1    | 29,245  |

| 19. DES                      | 16,176                 | 0.3    | 3,177   |

| 20. ECC                      | 339,046                | 7.0    | 66,581  |

| 21. MISTY1                   | 85,733                 | 1.8    | 16,836  |

| 22. RSA                      | 359,011                | 7.4    | 70,502  |

| 23. SASEBO_ALGO_INPUT        | 63,135                 | 1.3    | 12,398  |

| 24. SASEBO_ALGO_OUTPUT       | 33,143                 | 0.7    | 6,509   |

| 25. SASEBO_INPUT             | 2,400                  | 0.0    | 471     |

| 26. SASEBO_REG               | 127,903                | 2.6    | 25,117  |

| 27. SASEBO_VALUE             | 596                    | 0.0    | 117     |

| 28. SEED                     | 115,237                | 2.4    | 22,630  |

| 29. T DES                    | 27,127                 | 0.6    | 5,327   |

| Total cell area              | 4,830,232              | 100.0  | 948,555 |

1 ゲート = 2 入力 NAND ( $3.69\mu\text{m} \times 1.38\mu\text{m}$ )

表 4.6 Static Timing Analysis による LSI の動作速度

| 項目                | Worst (125°C 1.08V) | Typical (25°C 1.2V) | Best (-40°C 1.32V) |

|-------------------|---------------------|---------------------|--------------------|

| Maximum Frequency | 20.410 MHz          | 24.889 MHz          | 29.410 MHz         |

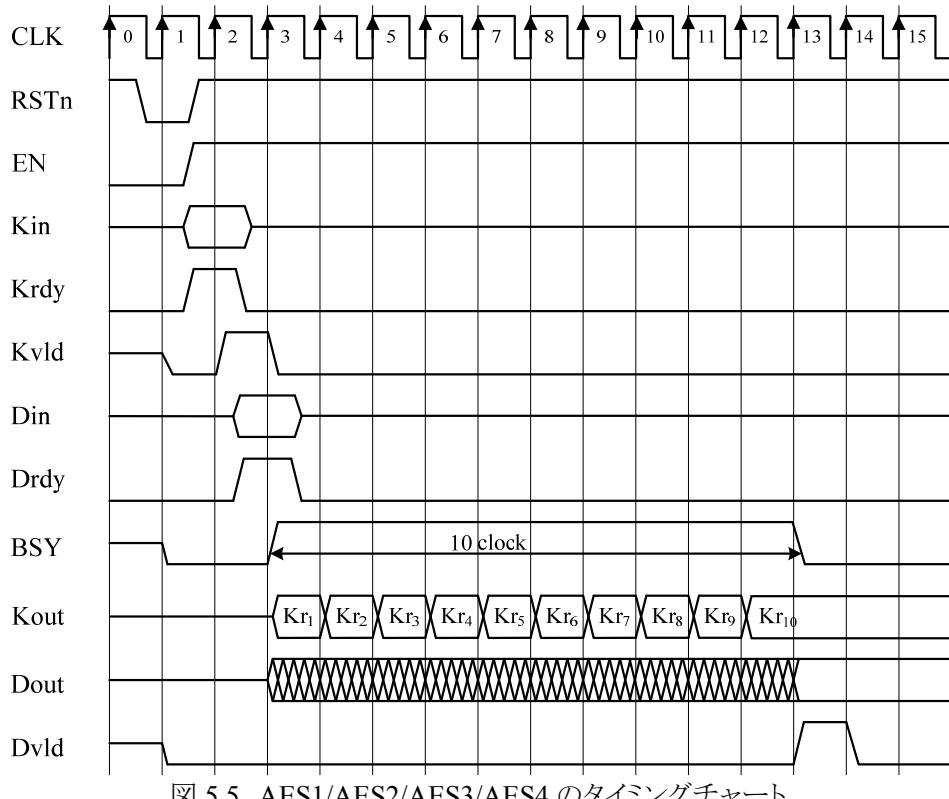

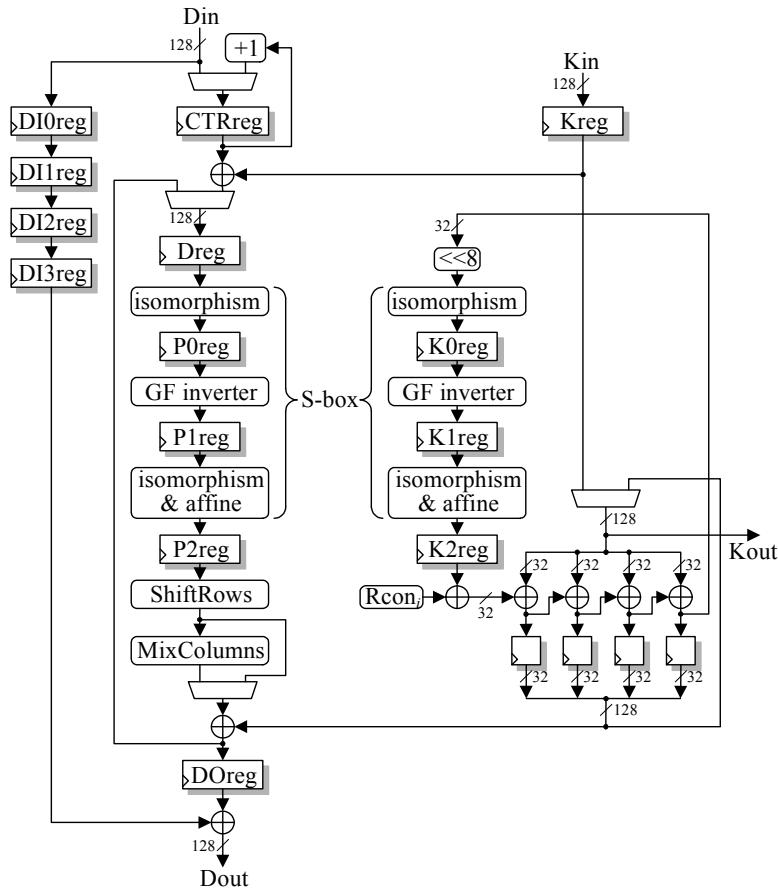

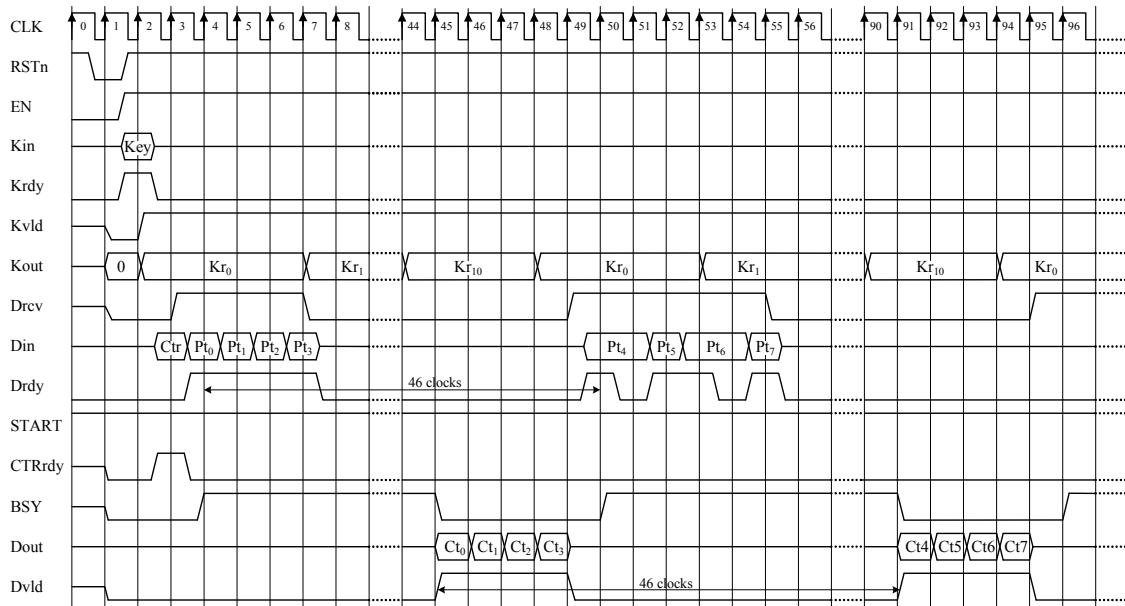

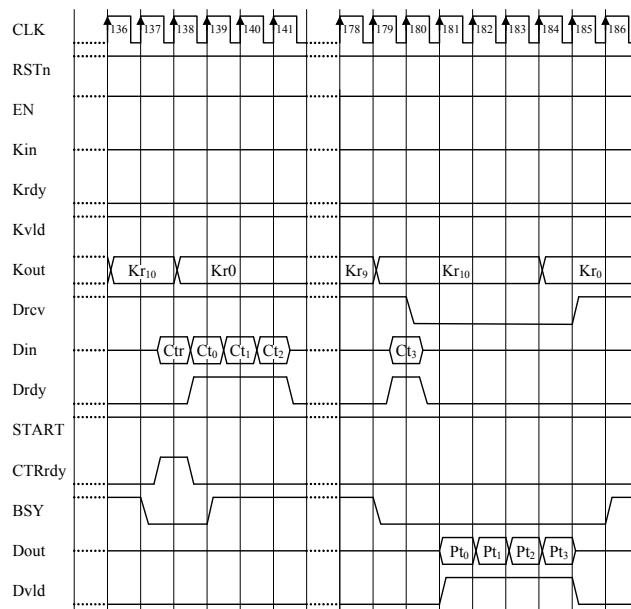

| Critical Path     | 48.995 ns           | 40.178 ns           | 33.993 ns          |