# ISO/IEC 18033-3 Standard Cryptographic LSI ~ with Side Channel Attack Countermeasures ~ Specification

- Version 1.0 -

September 25, 2009

Research Center for Information Security, National Institute of Advanced Industrial Science and Technology

## Index

## Page

| 1.  | OVER  | VIEW                                     | 1  |

|-----|-------|------------------------------------------|----|

| 2.  | EXTE  | RNAL INTERFACE                           | 2  |

|     | 2.1   | I/O Assignments                          | 2  |

|     | 2.2   | Control Interface                        | 12 |

| 3.  | INTE  | RNAL SPECIFICATIONS                      | 18 |

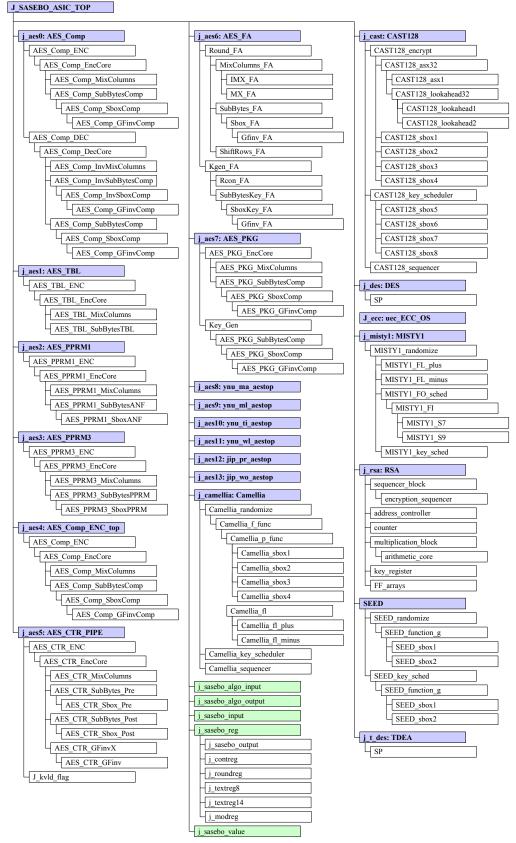

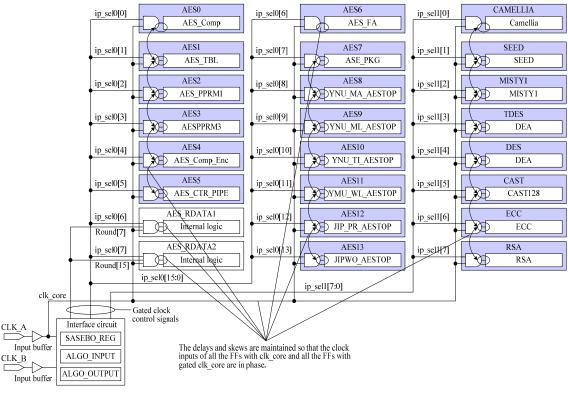

|     | 3.1   | Internal Structure of LSI                | 18 |

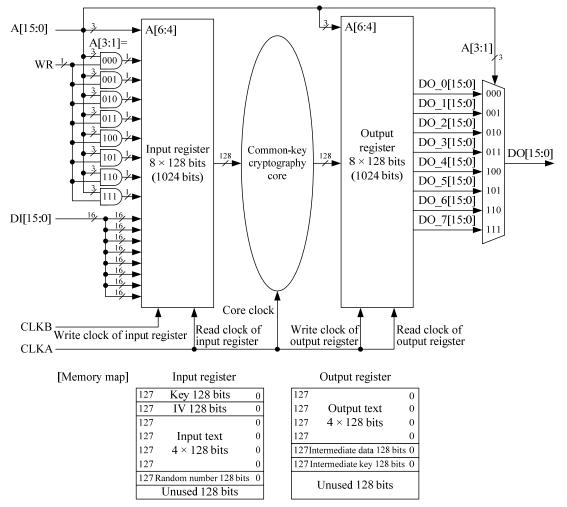

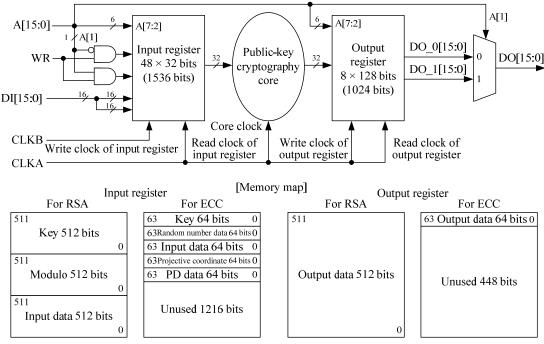

|     | 3.2   | Cryptographic Circuit Interface          | 21 |

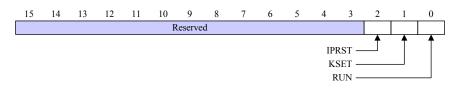

|     | 3.3   | Interface Registers                      | 22 |

|     | 3.4   | Clock Tree                               | 30 |

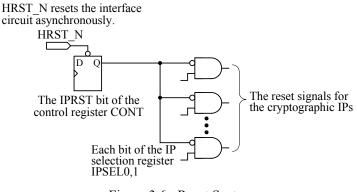

|     | 3.5   | Reset                                    | 30 |

|     | 3.6   | Supplementary Functions                  | 31 |

| 4.  | PHYS  | ICAL LAYOUT                              | 35 |

|     | 4.1   | 130-nm Version                           | 35 |

|     | 4.2   | 90-nm Version                            | 44 |

| 5.  | CRYP  | TOGRAPHIC HARDWARE IPs                   | 53 |

|     | 5.1   | AES0 (Composite Field S-box)             | 53 |

|     | 5.2   | AES1/AES2/AES3/AES4 (Variety of S-boxes) | 56 |

|     | 5.3   | AES5 (CTR Mode)                          | 58 |

|     | 5.4   | AES6 (FA Countermeasure)                 | 64 |

|     | 5.5   | AES7 (Round Key Pre-calculation)         |    |

|     | 5.6   | AES8 (MAO)                               | 70 |

|     | 5.7   | AES9 (MDPL)                              | 71 |

|     | 5.8   | AES10 (Threshold Implementation)         | 72 |

|     | 5.9   | AES11 (WDDL)                             |    |

|     | 5.10  | AES12/AES13 (Pseudo RSL)                 | 73 |

|     | 5.11  | Camellia                                 | 74 |

|     | 5.12  | CAST-128                                 | 77 |

|     | 5.13  | DES                                      | 79 |

|     | 5.14  | ECC                                      | 82 |

|     | 5.15  | MISTY1                                   | 85 |

|     | 5.16  | RSA                                      | 88 |

|     | 5.17  | SEED                                     | 92 |

|     | 5.18  | TDES                                     | 95 |

| REI | FEREN | CES                                      | 99 |

## 1. OVERVIEW

To evaluate Differential Power Analysis attacks and other implementation attacks, "The special purpose LSI implementing standard cryptographic algorithms" (hereinafter called the cryptographic LSI) implements the following cryptographic algorithms: public-key cryptography RSA, elliptic-curve cryptosystem (ECC), and every common-key cryptographic algorithm appearing in ISO/IEC 18033(Information technology – Security techniques – Encryption algorithms) Part 3: Block ciphers. The cryptographic LSI is manufactured using TSMC (Taiwan Semiconductor Manufacturing Company) 130nm or 90nm CMOS processes and packaged in a 160-pin ceramic QFP.

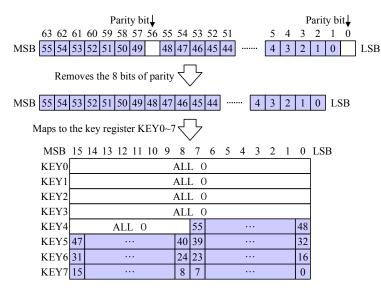

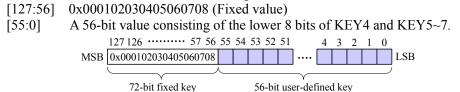

The LSI has the 9 algorithms including AES, which is implemented in 14 different ways, and houses 22 different cryptographic cores altogether. AES implementations No.8 through No.13 used custom logic synthesis. Because the LSI is intended not only for Japanese domestic use but also for use overseas, the key length for each algorithm is limited to meet the export control regulations; The upper 72 bits of the 128-bit secret keys in the block ciphers except for DES are fixed so that the user can only change the lower 56 bits. Similarly, RSA only supports a 512-bit key.

- AES (key length : 128 bits)

- No.0: S-Box implemented using composite field. Encryption and decryption.

- No.1: S-Box implemented using case statement. Encryption only.

- No.2: S-Box implemented using AND-XOR (1-Stage). Encryption only.

- No.3: S-Box implemented using AND-XOR (3-Stage). Encryption only.

- No.4: S-Box implemented using composite field. Encryption only.

- No.5: CTR mode supported. Pipelined.

- No.6: For fault-injection-attack resistance evaluation.

- No.7: Precalculation of round keys.

- No.8: For DPA countermeasure evaluation (Masked AND Operation).

- No.9: For DPA countermeasure evaluation (MDPL).

- No.10: For DPA countermeasure evaluation (Threshold Implementation).

- No.11: For DPA countermeasure evaluation (WDDL).

- No.12: For DPA countermeasure evaluation (Pseudo RSL).

- No.13: For DPA countermeasure evaluation (for Pseudo RSL effectiveness assessment).

The *n*-th implementation of AES will hereinafter be denoted as AESn. For example, No.5 of AES is AES5.

- Camellia (key length : 128 bits): Encryption and decryption.

- SEED: Encryption and decryption.

- MISTY1: Encryption and decryption.

- Triple-DES: 3 Key. Encryption and decryption.

- DES: Encryption and decryption.

- CAST128: Encryption and decryption.

- ECC (key length: 64 bits): Scalar multiplication on a point over a field of characteristic 2.

- RSA: 512-bit modular exponentiation operations.

The main functionalities of the LSI are as follows:

- Computes the cryptographic algorithms.

- Interfaces with Virtex-II PRO FPGA (xc2vp30) on SASEBO-R (Side-channel Attack Standard Evaluation Board) developed for mounting a cryptographic LSI in FY07.

- Generates a trigger signal for sampling information such as power consumption.

- Exports the pre-designated intermediate keys and algorithm values for fault attack evaluation (Only supported for AES6).

- Exports the intermediate keys and algorithm values on a fault event for fault attack evaluation (Only supported for AES6).

- Runs in the free-run mode that repeats cipher operations every 0.3 seconds (Only supported for AES0).

## 2. EXTERNAL INTERFACE

## 2.1 I/O Assignments

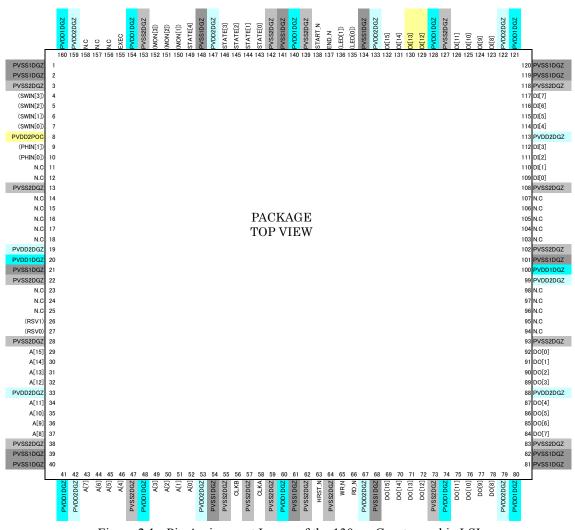

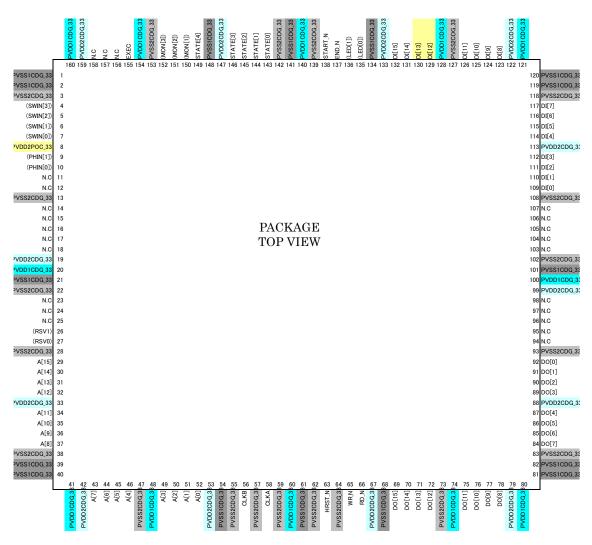

The I/O signals of the cryptographic LSI are listed in Table 2.1. Table 2.2 and Figure 2.1 show the assignments of the 160 pins of the 130nm LSI. Table 2.3 and Figure 2.2 represent the assignments of the 160 pins of the 90nm LSI. The 130nm and 90nm LSIs have identical package dimensions, pin assignments, and logic interfaces, but different core voltages  $(1.2 V \pm 0.12V \text{ and } 1.0V \pm 0.1V)$ . Parentheses in the "Signal Name" column denote the reserved signals for the future extension. The cryptographic LSI does not use those signals. For VSS/VDD pins, the "Signal Name" column lists the corresponding cell names. The LSI has the separated VDD/VSS pins for internal circuits and I/O buffers to reduce noise and to enable precise measurements of power consumption or electromagnetic emission while computing cryptographic algorithms.

| Type<br>(No. of signals) | Signal name | No. of signals | Active<br>H/L | Direction | Purpose/Description                                                                              |

|--------------------------|-------------|----------------|---------------|-----------|--------------------------------------------------------------------------------------------------|

|                          | CLKA        | 1              |               | IN        | Clock input of 24 MHz for<br>intra-LSI circuit. Must be the same<br>as CLKB or higher frequency. |

| System                   | CLKB        | 1              |               | IN        | Clock input for LSI interface circuit                                                            |

| System<br>(11)           | HRST_N      | 1              | L             | IN        | Reset signal generated by on-board reset circuit. Asynchronous reset input.                      |

|                          | LEDO[1:0]   | 2              | L             | OUT       | LED driver outputs (NC pins)                                                                     |

|                          | SWIN[3:0]   | 4              |               | IN        | Switch inputs (NC pins)                                                                          |

|                          | PHIN[1:0]   | 2              |               | IN        | Pin header inputs (NC pins)                                                                      |

|                          | WR_N        | 1              | L             | IN        | Write                                                                                            |

| Bus control              | RD_N        | 1              | L             | IN        | Read                                                                                             |

| (4)                      | RSV0        | 1              |               | IN        | (NC pins)                                                                                        |

|                          | RSV1        | 1              |               | IN        | (NC pins)                                                                                        |

| Bus address (16)         | A[15:0]     | 16             |               | IN        |                                                                                                  |

| Bus data                 | DI[15:0]    | 16             |               | IN        | Input data                                                                                       |

| (32)                     | DO[15:0]    | 16             |               | OUT       | Output data                                                                                      |

|                          | START_N     | 1              | L             | OUT       | Start of target operation                                                                        |

|                          | END_N       | 1              | L             | OUT       | End of target operation                                                                          |

| Evaluation               | (TRIG0)     | 1              |               | OUT       | (NC pins)                                                                                        |

| (13)                     | (TRIG1)     | 1              |               | OUT       | (NC pins)                                                                                        |

| (15)                     | EXEC        | 1              | Н             | OUT       | Indicates target in processing                                                                   |

|                          | STATE[3:0]  | 4              |               | OUT       | Indicates selected IP                                                                            |

|                          | MON[3:0]    | 4              |               | OUT       | Internal monitor use (TBD)                                                                       |

| Total                    |             | 77             |               |           |                                                                                                  |

| Table | 2.1 | I/O | Signals |  |

|-------|-----|-----|---------|--|

| T C   |     |     |         |  |

| Pin No | Signal name | I/O | I/F voltage | Output | I/O buffer | Function    |

|--------|-------------|-----|-------------|--------|------------|-------------|

| 1      | PVSS1DGZ    |     | 0           |        |            | core GND    |

| 2      | PVSS1DGZ    |     |             |        |            | core GND    |

| 3      | PVSS2DGZ    |     |             |        |            | I/O GND     |

| 4      | (SWIN[3])   |     |             |        |            | N.C         |

| 5      | (SWIN[2])   |     |             |        |            | N.C         |

| 6      | (SWIN[1])   |     |             |        |            | N.C         |

| 7      | (SWIN[0])   |     |             |        |            | N.C         |

| 8      | PVDD2POC    |     |             |        |            | I/O 3.3V    |

| 9      | (PHIN[1])   |     |             |        |            | N.C         |

| 10     | (PHIN[0])   |     |             |        |            | N.C         |

| 11     | N.C         |     |             |        |            | N.C         |

| 12     | N.C         |     |             |        |            | N.C         |

| 13     | PVSS2DGZ    |     |             |        |            | I/O GND     |

| 14     | N.C         |     |             |        |            | N.C         |

| 15     | N.C         |     |             |        |            | N.C         |

| 16     | N.C         |     |             |        |            | N.C         |

| 17     | N.C         |     |             |        |            | N.C         |

| 18     | N.C         |     |             |        |            | N.C         |

| 19     | PVDD2DGZ    |     |             |        |            | I/O 3.3V    |

| 20     | PVDD1DGZ    |     |             |        |            | core 1.2V   |

| 21     | PVSS1DGZ    |     |             |        |            | core GND    |

| 22     | PVSS2DGZ    |     |             |        |            | I/O GND     |

| 23     | N.C         |     |             |        |            | N.C         |

| 24     | N.C         |     |             |        |            | N.C         |

| 25     | N.C         |     |             |        |            | N.C         |

| 26     | (RSV1)      |     |             |        |            | N.C         |

| 27     | (RSV0)      |     |             |        |            | N.C         |

| 28     | PVSS2DGZ    |     |             |        |            | I/O GND     |

| 29     | A[15]       | Ι   | 3.3V        |        | PDIDGZ     | Address Bus |

| 30     | A[14]       | Ι   | 3.3V        |        | PDIDGZ     | Address Bus |

| 31     | A[13]       | Ι   | 3.3V        |        | PDIDGZ     | Address Bus |

| 32     | A[12]       | Ι   | 3.3V        |        | PDIDGZ     | Address Bus |

| 33     | PVDD2DGZ    |     |             |        |            | I/O 3.3V    |

| 34     | A[11]       | Ι   | 3.3V        |        | PDIDGZ     | Address Bus |

| 35     | A[10]       | Ι   | 3.3V        |        | PDIDGZ     | Address Bus |

| 36     | A[9]        | Ι   | 3.3V        |        | PDIDGZ     | Address Bus |

| 37     | A[8]        | Ι   | 3.3V        |        | PDIDGZ     | Address Bus |

| 38     | PVSS2DGZ    |     |             |        |            | I/O GND     |

| 39     | PVSS1DGZ    |     |             |        |            | core GND    |

| 40     | PVSS1DGZ    |     |             |        |            | core GND    |

Table 2.2 Pin Assignments of the 130-nm LSI (1/4)

| Pin No | Signal name | I/O | I/F voltage | Output | I/O buffer | Function       |

|--------|-------------|-----|-------------|--------|------------|----------------|

| 41     | PVDD1DGZ    |     |             |        |            | core 1.2V      |

| 42     | PVDD2DGZ    |     |             |        |            | I/O 3.3V       |

| 43     | A[7]        | Ι   | 3.3V        |        | PDIDGZ     | Address Bus    |

| 44     | A[6]        | Ι   | 3.3V        |        | PDIDGZ     | Address Bus    |

| 45     | A[5]        | Ι   | 3.3V        |        | PDIDGZ     | Address Bus    |

| 46     | A[4]        | Ι   | 3.3V        |        | PDIDGZ     | Address Bus    |

| 47     | PVSS2DGZ    |     |             |        |            | I/O GND        |

| 48     | PVDD1DGZ    |     |             |        |            | core 1.2V      |

| 49     | A[3]        | Ι   | 3.3V        |        | PDIDGZ     | Address Bus    |

| 50     | A[2]        | Ι   | 3.3V        |        | PDIDGZ     | Address Bus    |

| 51     | A[1]        | Ι   | 3.3V        |        | PDIDGZ     | Address Bus    |

| 52     | A[0]        | Ι   | 3.3V        |        | PDIDGZ     | Address Bus    |

| 53     | PVDD2DGZ    |     |             |        |            | I/O 3.3V       |

| 54     | PVSS1DGZ    |     |             |        |            | core GND       |

| 55     | PVSS2DGZ    |     |             |        |            | I/O GND        |

| 56     | CLKB        | Ι   | 3.3V        |        | PDISDGZ    | Clock. Schmitt |

| 57     | PVSS2DGZ    |     |             |        |            | I/O GND        |

| 58     | CLKA        | Ι   | 3.3V        |        | PDISDGZ    | Clock. Schmitt |

| 59     | PVSS2DGZ    |     |             |        |            | I/O GND        |

| 60     | PVDD1DGZ    |     |             |        |            | core 1.2V      |

| 61     | PVSS1DGZ    |     |             |        |            | core GND       |

| 62     | PVSS2DGZ    |     |             |        |            | I/O GND        |

| 63     | HRST_N      | Ι   | 3.3V        |        | PDISDGZ    | Reset. Schmitt |

| 64     | PVSS2DGZ    |     |             |        |            | I/O GND        |

| 65     | WR_N        | Ι   | 3.3V        |        | PDIDGZ     | Write          |

| 66     | RD_N        | Ι   | 3.3V        |        | PDIDGZ     | Read           |

| 67     | PVDD2DGZ    |     |             |        |            | I/O 3.3V       |

| 68     | PVSS1DGZ    |     |             |        |            | core GND       |

| 69     | DO[15]      | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data    |

| 70     | DO[14]      | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data    |

| 71     | DO[13]      | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data    |

| 72     | DO[12]      | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data    |

| 73     | PVSS2DGZ    |     |             |        |            | I/O GND        |

| 74     | PVDD1DGZ    |     |             |        |            | core 1.2V      |

| 75     | DO[11]      | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data    |

| 76     | DO[10]      | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data    |

| 77     | DO[9]       | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data    |

| 78     | DO[8]       | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data    |

| 79     | PVDD2DGZ    |     |             |        |            | I/O 3.3V       |

| 80     | PVDD1DGZ    |     |             |        |            | core 1.2V      |

Table 2.2 Pin Assignments of the 130-nm LSI (2/4)

| Pin No | Signal name | I/O | I/F voltage | Output | I/O buffer | Function    |

|--------|-------------|-----|-------------|--------|------------|-------------|

| 81     | PVSS1DGZ    |     | <u> </u>    |        |            | core GND    |

| 82     | PVSS1DGZ    |     |             |        |            | core GND    |

| 83     | PVSS2DGZ    |     |             |        |            | I/O GND     |

| 84     | DO[7]       | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data |

| 85     | DO[6]       | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data |

| 86     | DO[5]       | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data |

| 87     | DO[4]       | Ο   | 3.3V        | 8mA    | PDO08CDG   | Output Data |

| 88     | PVDD2DGZ    |     |             |        |            | I/O 3.3V    |

| 89     | DO[3]       | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data |

| 90     | DO[2]       | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data |

| 91     | DO[1]       | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data |

| 92     | DO[0]       | 0   | 3.3V        | 8mA    | PDO08CDG   | Output Data |

| 93     | PVSS2DGZ    |     |             |        |            | I/O GND     |

| 94     | N.C         |     |             |        |            | N.C         |

| 95     | N.C         |     |             |        |            | N.C         |

| 96     | N.C         |     |             |        |            | N.C         |

| 97     | N.C         |     |             |        |            | N.C         |

| 98     | N.C         |     |             |        |            | N.C         |

| 99     | PVDD2DGZ    |     |             |        |            | I/O 3.3V    |

| 100    | PVDD1DGZ    |     |             |        |            | core 1.2V   |

| 101    | PVSS1DGZ    |     |             |        |            | core GND    |

| 102    | PVSS2DGZ    |     |             |        |            | I/O GND     |

| 103    | N.C         |     |             |        |            | N.C         |

| 104    | N.C         |     |             |        |            | N.C         |

| 105    | N.C         |     |             |        |            | N.C         |

| 106    | N.C         |     |             |        |            | N.C         |

| 107    | N.C         |     |             |        |            | N.C         |

| 108    | PVSS2DGZ    |     |             |        |            | I/O GND     |

| 109    | DI[0]       | Ι   | 3.3V        |        | PDIDGZ     | Input Data  |

| 110    | DI[1]       | Ι   | 3.3V        |        | PDIDGZ     | Input Data  |

| 111    | DI[2]       | Ι   | 3.3V        |        | PDIDGZ     | Input Data  |

| 112    | DI[3]       | Ι   | 3.3V        |        | PDIDGZ     | Input Data  |

| 113    | PVDD2DGZ    |     |             |        |            | I/O 3.3V    |

| 114    | DI[4]       | Ι   | 3.3V        |        | PDIDGZ     | Input Data  |

| 115    | DI[5]       | Ι   | 3.3V        |        | PDIDGZ     | Input Data  |

| 116    | DI[6]       | Ι   | 3.3V        |        | PDIDGZ     | Input Data  |

| 117    | DI[7]       | Ι   | 3.3V        |        | PDIDGZ     | Input Data  |

| 118    | PVSS2DGZ    |     |             |        |            | I/O GND     |

| 119    | PVSS1DGZ    |     |             |        |            | core GND    |

| 120    | PVSS1DGZ    |     |             |        |            | core GND    |

Table 2.2 Pin Assignments of the 130-nm LSI (3/4)

| Pin No | Signal name | I/O | I/F voltage | Output | I/O buffer | Function           |

|--------|-------------|-----|-------------|--------|------------|--------------------|

| 121    | PVDD1DGZ    |     |             |        |            | core 1.2V          |

| 122    | PVDD2DGZ    |     |             |        |            | I/O 3.3V           |

| 123    | DI[8]       | Ι   | 3.3V        |        | PDIDGZ     | Input Data         |

| 124    | DI[9]       | Ι   | 3.3V        |        | PDIDGZ     | Input Data         |

| 125    | DI[10]      | Ι   | 3.3V        |        | PDIDGZ     | Input Data         |

| 126    | DI[11]      | Ι   | 3.3V        |        | PDIDGZ     | Input Data         |

| 127    | PVSS2DGZ    |     |             |        |            | I/O GND            |

| 128    | PVDD1DGZ    |     |             |        |            | core 1.2V          |

| 129    | DI[12]      | Ι   | 3.3V        |        | PDIDGZ     | Input Data         |

| 130    | DI[13]      | Ι   | 3.3V        |        | PDIDGZ     | Input Data         |

| 131    | DI[14]      | Ι   | 3.3V        |        | PDIDGZ     | Input Data         |

| 132    | DI[15]      | Ι   | 3.3V        |        | PDIDGZ     | Input Data         |

| 133    | PVDD2DGZ    |     |             |        |            | I/O 3.3V           |

| 134    | PVSS1DGZ    |     |             |        |            | core GND           |

| 135    | (LED[0])    |     |             |        |            | N.C                |

| 136    | (LED[1])    |     |             |        |            | N.C                |

| 137    | END_N       | 0   | 3.3V        | 8mA    | PDO08CDG   | End of Operation   |

| 138    | START_N     | 0   | 3.3V        | 8mA    | PDO08CDG   | Start of Operation |

| 139    | PVSS2DGZ    |     |             |        |            | I/O GND            |

| 140    | PVDD1DGZ    |     |             |        |            | core 1.2V          |

| 141    | PVSS1DGZ    |     |             |        |            | core GND           |

| 142    | PVSS2DGZ    |     |             |        |            | I/O GND            |

| 143    | STATE[0]    | 0   | 3.3V        | 8mA    | PDO08CDG   | Selected IP        |

| 144    | STATE[1]    | 0   | 3.3V        | 8mA    | PDO08CDG   | Selected IP        |

| 145    | STATE[2]    | 0   | 3.3V        | 8mA    | PDO08CDG   | Selected IP        |

| 146    | STATE[3]    | 0   | 3.3V        | 8mA    | PDO08CDG   | Selected IP        |

| 147    | PVDD2DGZ    |     |             |        |            | I/O 3.3V           |

| 148    | PVSS1DGZ    |     |             |        |            | core GND           |

| 149    | (MON[0])    |     |             |        |            | N.C                |

| 150    | (MON[1])    |     |             |        |            | N.C                |

| 151    | (MON[2])    |     |             |        |            | N.C                |

| 152    | (MON[3])    |     |             |        |            | N.C                |

| 153    | PVSS2DGZ    |     |             |        |            | I/O GND            |

| 154    | PVDD1DGZ    |     |             |        |            | core 1.2V          |

| 155    | EXEC        | 0   | 3.3V        | 8mA    | PDO08CDG   | In Processing      |

| 156    | N.C         |     |             |        |            | N.C                |

| 157    | N.C         |     |             |        |            | N.C                |

| 158    | N.C         |     |             |        |            | N.C                |

| 159    | PVDD2DGZ    |     |             |        |            | I/O 3.3V           |

| 160    | PVDD1DGZ    |     |             |        |            | core 1.2V          |

Table 2.2 Pin Assignments of the 130-nm LSI (4/4)

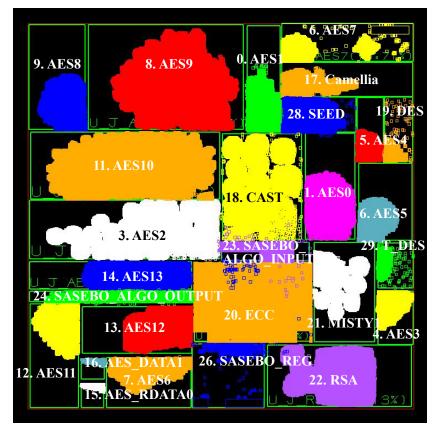

Figure 2.1 Pin Assignment Image of the 130nm Cryptographic LSI

| Pin No |             |          | I/F voltage | I/O buffer        | Function    |

|--------|-------------|----------|-------------|-------------------|-------------|

| 1      | PVSS1CDG 33 |          |             |                   | core GND    |

| 2      | PVSS1CDG 33 |          |             |                   | core GND    |

| 3      | PVSS2CDG 33 |          |             |                   | I/O GND     |

| 4      | (SWIN[3])   |          |             |                   | N.C         |

| 5      | (SWIN[2])   |          |             |                   | N.C         |

| 6      | (SWIN[1])   |          |             |                   | N.C         |

| 7      | (SWIN[0])   |          |             |                   | N.C         |

| 8      | PVDD2POC 33 |          |             |                   | I/O 3.3V    |

| 9      | (PHIN[1])   |          |             |                   | N.C         |

| 10     | (PHIN[0])   |          |             |                   | N.C         |

| 11     | N.C         |          |             |                   | N.C         |

| 12     | N.C         |          |             |                   | N.C         |

| 13     | PVSS2CDG_33 |          |             |                   | I/O GND     |

| 14     | N.C         |          |             |                   | N.C         |

| 15     | N.C         |          |             |                   | N.C         |

| 16     | N.C         |          |             |                   | N.C         |

| 17     | N.C         |          |             |                   | N.C         |

| 18     | N.C         |          |             |                   | N.C         |

| 19     | PVDD2CDG_33 |          |             |                   | I/O 3.3V    |

| 20     | PVDD1CDG_33 |          |             |                   | core 1.0V   |

| 21     | PVSS1CDG_33 |          |             |                   | core GND    |

| 22     | PVSS2CDG_33 |          |             |                   | I/O GND     |

| 23     | N.C         |          |             |                   | N.C         |

| 24     | N.C         |          |             |                   | N.C         |

| 25     | N.C         |          |             |                   | N.C         |

| 26     | (RSV1)      |          |             |                   | N.C         |

| 27     | (RSV0)      |          |             |                   | N.C         |

| 28     | PVSS2CDG_33 | -        |             |                   | I/O GND     |

| 29     | A[15]       | I        | 3.3V        | PDC0816CDG_33     | Address Bus |

| 30     | A[14]       | I        | 3.3V        | <br>PDC0816CDG_33 | Address Bus |

| 31     | A[13]       | I        | 3.3V        | <br>PDC0816CDG_33 | Address Bus |

| 32     | A[12]       | Ι        | 3.3V        | <br>PDC0816CDG_33 | Address Bus |

| 33     | PVDD2CDG_33 | <b>.</b> | 2.237       |                   | I/O 3.3V    |

| 34     | A[11]       | I        | 3.3V        | <br>PDC0816CDG_33 | Address Bus |

| 35     | A[10]       | I<br>T   | 3.3V        | <br>PDC0816CDG_33 | Address Bus |

| 36     | A[9]        | I        | 3.3V        | <br>PDC0816CDG_33 | Address Bus |

| 37     | A[8]        | Ι        | 3.3V        | PDC0816CDG_33     | Address Bus |

| 38     | PVSS2CDG_33 |          |             |                   | I/O GND     |

| 39     | PVSS1CDG_33 |          |             |                   | core GND    |

| 40     | PVSS1CDG_33 |          |             |                   | core GND    |

Table 2.3

Pin Assignment of the 90-nm LSI (1/4)

| Pin No |             |      | I/F voltage |     | I/O buffer    | Function             |

|--------|-------------|------|-------------|-----|---------------|----------------------|

| 41     | PVDD1CDG 33 | _, _ |             |     |               | core 1.0V            |

| 42     | PVDD2CDG 33 |      |             |     |               | I/O 3.3V             |

| 43     | A[7]        | Ι    | 3.3V        |     | PDC0816CDG 33 | Address Bus          |

| 44     | A[6]        | Ι    | 3.3V        |     | PDC0816CDG 33 | Address Bus          |

| 45     | A[5]        | Ι    | 3.3V        |     | PDC0816CDG 33 | Address Bus          |

| 46     | A[4]        | Ι    | 3.3V        |     | PDC0816CDG 33 | Address Bus          |

| 47     | PVSS2CDG 33 |      |             |     |               | I/O GND              |

| 48     | PVDD1CDG 33 |      |             |     |               | core 1.2V            |

| 49     | A[3]        | Ι    | 3.3V        |     | PDC0816CDG 33 | Address Bus          |

| 50     | A[2]        | Ι    | 3.3V        |     | PDC0816CDG_33 | Address Bus          |

| 51     | A[1]        | Ι    | 3.3V        |     | PDC0816CDG_33 | Address Bus          |

| 52     | A[0]        | Ι    | 3.3V        |     | PDC0816CDG_33 | Address Bus          |

| 53     | PVDD2CDG_33 |      |             |     |               | I/O 3.3V             |

| 54     | PVSS1CDG_33 |      |             |     |               | core GND             |

| 55     | PVSS2CDG_33 |      |             |     |               | I/O GND              |

| 56     | CLKB        | Ι    | 3.3V        |     | PDS0816CDG_33 | Clock. Schmitt       |

| 57     | PVSS2CDG_33 |      |             |     |               | I/O GND              |

| 58     | CLKA        | Ι    | 3.3V        |     | PDS0816CDG_33 | Clock. Schmitt       |

| 59     | PVSS2CDG_33 |      |             |     |               | I/O GND              |

| 60     | PVDD1CDG_33 |      |             |     |               | core VDD (1.2V/1.0V) |

| 61     | PVSS1CDG_33 |      |             |     |               | core GND             |

| 62     | PVSS2CDG_33 |      |             |     |               | I/O GND              |

| 63     | HRST_N      | Ι    | 3.3V        |     | PDS0816CDG_33 | Reset. Schmitt       |

| 64     | PVSS2CDG_33 |      |             |     |               | I/O GND              |

| 65     | WR_N        | Ι    | 3.3V        |     | PDC0816CDG_33 | Write                |

| 66     | RD_N        | Ι    | 3.3V        |     | PDC0816CDG_33 | Read                 |

| 67     | PVDD2CDG_33 |      |             |     |               | I/O 3.3V             |

| 68     | PVSS1CDG_33 |      |             |     |               | core GND             |

| 69     | DO[15]      | 0    | 3.3V        | 8mA | PDC0816CDG_33 | Output Data          |

| 70     | DO[14]      | 0    | 3.3V        | 8mA | PDC0816CDG_33 | Output Data          |

| 71     | DO[13]      | 0    | 3.3V        | 8mA | PDC0816CDG_33 | Output Data          |

| 72     | DO[12]      | 0    | 3.3V        | 8mA | PDC0816CDG_33 | Output Data          |

| 73     | PVSS2CDG_33 |      |             |     |               | I/O GND              |

| 74     | PVDD1CDG_33 |      |             |     |               | core VDD (1.2V/1.0V) |

| 75     | DO[11]      | 0    | 3.3V        | 8mA | PDC0816CDG_33 | Output Data          |

| 76     | DO[10]      | 0    | 3.3V        | 8mA | PDC0816CDG_33 | Output Data          |

| 77     | DO[9]       | 0    | 3.3V        | 8mA | PDC0816CDG_33 | Output Data          |

| 78     | DO[8]       | 0    | 3.3V        | 8mA | PDC0816CDG_33 | Output Data          |

| 79     | PVDD2CDG_33 |      |             |     |               | I/O 3.3V             |

| 80     | PVDD1CDG_33 |      |             |     |               | core VDD (1.2V/1.0V) |

Table 2.3 Pin Assignment of the 90-nm LSI (2/4)

| Pin No | Signal name | I/O | I/F voltage |     | I/O buffer         | Function      |

|--------|-------------|-----|-------------|-----|--------------------|---------------|

| 81     | PVSS1CDG 33 |     | 0           |     |                    | core GND      |

| 82     | PVSS1CDG 33 |     |             |     |                    | core GND      |

| 83     | PVSS2CDG 33 |     |             |     |                    | I/O GND       |

|        | DO[7]       | 0   | 3.3V        | 8mA | PDC0816CDG 33      | Output Data   |

|        | DO[6]       | 0   | 3.3V        | 8mA | PDC0816CDG 33      | Output Data   |

| 86     | DO[5]       | 0   | 3.3V        | 8mA | PDC0816CDG 33      | Output Data   |

| 87     | DO[4]       | 0   | 3.3V        | 8mA | PDC0816CDG 33      | Output Data   |

| 88     | PVDD2CDG 33 |     |             |     |                    | I/O 3.3V      |

| 89     | DO[3]       | Ο   | 3.3V        | 8mA | PDC0816CDG 33      | Output Data   |

| 90     | DO[2]       | 0   | 3.3V        | 8mA | PDC0816CDG_33      | Output Data   |

| 91     | DO[1]       | 0   | 3.3V        | 8mA | PDC0816CDG_33      | Output Data   |

| 92     | DO[0]       | 0   | 3.3V        | 8mA | PDC0816CDG_33      | Output Data   |

| 93     | PVSS2CDG_33 |     |             |     |                    | I/O GND       |

| 94     | N.C         |     |             |     |                    | N.C           |

| 95     | N.C         |     |             |     |                    | N.C           |

|        | N.C         |     |             |     |                    | N.C           |

|        | N.C         |     |             |     |                    | N.C           |

| 98     | N.C         |     |             |     |                    | N.C           |

| 99     | PVDD2CDG_33 |     |             |     |                    | I/O 3.3V      |

|        | PVDD1CDG_33 |     |             |     |                    | core VDD 1.0V |

| 101    | PVSS1CDG_33 |     |             |     |                    | core GND      |

| 102    | PVSS2CDG_33 |     |             |     |                    | I/O GND       |

| 103    | N.C         |     |             |     |                    | N.C           |

| 104    | N.C         |     |             |     |                    | N.C           |

|        | N.C         |     |             |     |                    | N.C           |

|        | N.C         |     |             |     |                    | N.C           |

|        | N.C         |     |             |     |                    | N.C           |

|        | PVSS2CDG_33 |     |             |     | PD 0001 ( 57 5 1 ) | I/O GND       |

|        | DI[0]       | I   | 3.3V        |     | PDC0816CDG_33      | Input Data    |

|        | DI[1]       | I   | 3.3V        |     | PDC0816CDG_33      | Input Data    |

|        | DI[2]       | I   | 3.3V        |     | PDC0816CDG_33      | Input Data    |

|        | DI[3]       | Ι   | 3.3V        |     | PDC0816CDG_33      | Input Data    |

| 113    | PVDD2CDG_33 |     | 2 237       |     |                    | I/O 3.3V      |

|        | DI[4]       | I   | 3.3V        |     | PDC0816CDG 33      | Input Data    |

|        | DI[5]       | l   | 3.3V        |     | PDC0816CDG_33      | Input Data    |

|        | DI[6]       | I   | 3.3V        |     | PDC0816CDG_33      | Input Data    |

|        | DI[7]       | Ι   | 3.3V        |     | PDC0816CDG_33      | Input Data    |

|        | PVSS2CDG_33 |     |             |     |                    | I/O GND       |

|        | PVSS1CDG_33 |     |             |     |                    | core GND      |

| 120    | PVSS1CDG_33 |     |             |     |                    | core GND      |

Table 2.3 Pin Assignment of the 90-nm LSI (3/4)

| Pin No | ·           |   | I/F voltage |     | I/O buffer    | Function           |

|--------|-------------|---|-------------|-----|---------------|--------------------|

| 121    | PVDD1CDG 33 |   |             |     |               | core 1.0V          |

| 122    | PVDD2CDG 33 |   |             |     |               | I/O 3.3V           |

| 123    | DI[8]       | Ι | 3.3V        |     | PDC0816CDG 33 | Input Data         |

| 124    | DI[9]       | Ι | 3.3V        |     | PDC0816CDG_33 | Input Data         |

| 125    | DI[10]      | Ι | 3.3V        |     | PDC0816CDG_33 | Input Data         |

| 126    | DI[11]      | Ι | 3.3V        |     | PDC0816CDG_33 | Input Data         |

| 127    | PVSS2CDG_33 |   |             |     |               | I/O GND            |

| 128    | PVDD1CDG_33 |   |             |     |               | core 1.0V          |

| 129    | DI[12]      | Ι | 3.3V        |     | PDC0816CDG_33 | Input Data         |

| 130    | DI[13]      | Ι | 3.3V        |     | PDC0816CDG_33 | Input Data         |

| 131    | DI[14]      | Ι | 3.3V        |     | PDC0816CDG_33 | Input Data         |

| 132    | DI[15]      | Ι | 3.3V        |     | PDC0816CDG_33 | Input Data         |

| 133    | PVDD2CDG_33 |   |             |     |               | I/O 3.3V           |

| 134    | PVSS1CDG_33 |   |             |     |               | core GND           |

| 135    | (LED[0])    |   |             |     |               | N.C                |

| 136    | (LED[1])    |   |             |     |               | N.C                |

| 137    | END_N       | 0 | 3.3V        | 8mA | PDC0816CDG_33 | End of Operation   |

| 138    | START_N     | 0 | 3.3V        | 8mA | PDC0816CDG_33 | Start of Operation |

| 139    | PVSS2CDG_33 |   |             |     |               | I/O GND            |

| 140    | PVDD1CDG_33 |   |             |     |               | core 1.0V          |

| 141    | PVSS1CDG_33 |   |             |     |               | core GND           |

| 142    | PVSS2CDG_33 |   |             |     |               | I/O GND            |

| 143    | STATE[0]    | 0 | 3.3V        | 8mA | PDC0816CDG_33 | Selected IP        |

| 144    | STATE[1]    | 0 | 3.3V        | 8mA | PDC0816CDG_33 | Selected IP        |

| 145    | STATE[2]    | 0 | 3.3V        | 8mA | PDC0816CDG_33 | Selected IP        |

| 146    | STATE[3]    | 0 | 3.3V        | 8mA | PDC0816CDG_33 | Selected IP        |

| 147    | PVDD2CDG_33 |   |             |     |               | I/O 3.3V           |

| 148    | PVSS1CDG_33 |   |             |     |               | core GND           |

| 149    | STATE[4]    |   |             |     | PDC0816CDG_33 | N.C                |

| 150    | (MON[1])    |   |             |     |               | N.C                |

| 151    | (MON[2])    |   |             |     |               | N.C                |

| 152    | (MON[3])    |   |             |     |               | N.C                |

| 153    | PVSS2CDG_33 |   |             |     |               | I/O GND            |

| 154    | PVDD1CDG_33 |   | 2.237       | 0   |               | core 1.0V          |

|        | EXEC        | 0 | 3.3V        | 8mA | PDC0816CDG_33 | In Processing      |

| 156    | N.C         |   |             |     |               | N.C                |

| 157    | N.C         |   |             |     |               | N.C                |

| 158    | N.C         |   |             |     |               | N.C                |

| 159    | PVDD2CDG_33 |   |             |     |               | I/O 3.3V           |

| 160    | PVDD1CDG_33 |   |             |     |               | core 1.0V          |

Table 2.3 Pin Assignment of the 90-nm LSI (4/4)

Figure 2.2 Pin Assignment Image of the 90nm Cryptographic LSI

## 2.2 Control Interface

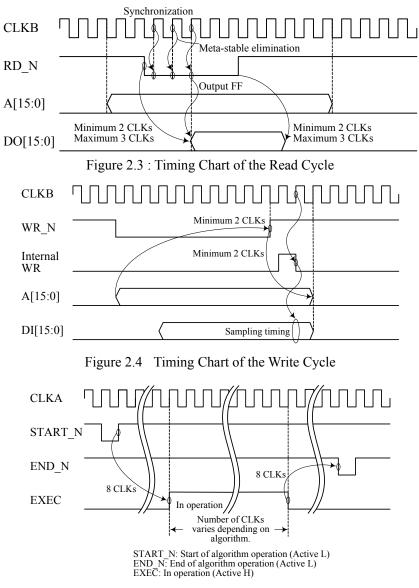

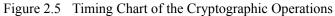

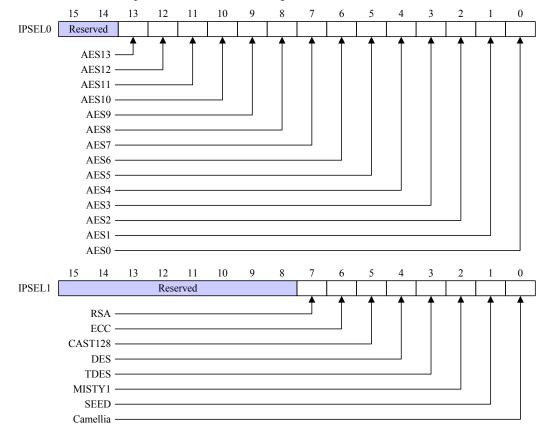

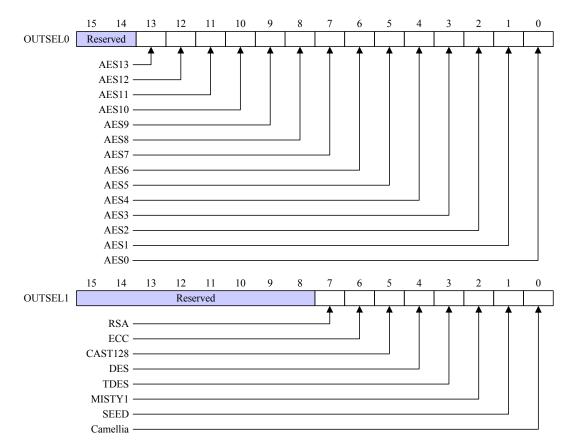

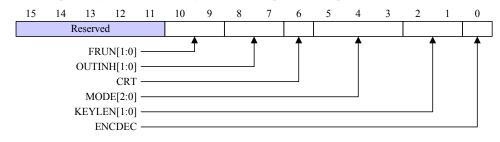

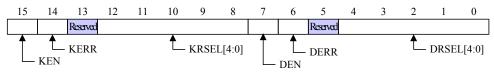

Table 2.4 lists the interface registers and address map of the cryptographic LSI. Figure 2.3, Figure 2.4, and Figure 2.5 chart the data read and write timings on the registers. Through the interface registers, the sequence described below controls each cryptographic IP core. Refer to Section 3.3 for a detailed description of the interface registers.

- Cryptographic algorithm cores other than AES5

- (a) Operating IP selection : Set the corresponding bits on the IP selection register (IPSEL0, 1).

- (b) Selected IP reset : Write 1 then 0 to CONT[IPRST].

- (c) Output IP selection : Set the corresponding bit on the output selection register (OUTSEL0, 1).

- (d) Mode setting : Set desired operating modes on the mode register(MODE). (\*1)

- (e) Key setting :

- 1. Set KEY0~7 for the common-key ciphers, EXP0~31 and MOD0~31 for RSA, or IDATA0~3 for ECC.

- 2. Set CONT[KSET], then wait until this bit is cleared.

- (f) Initial value (IV) setting : Set IV0~7. (\*2)

- (g) Random number (seed) setting : Set RAND0~7. (\*3)

- (h) Cryptographic operation : Repeat the following sequence.

- 1. Set ITEXT0~7(\*4) for the common-key ciphers, IDATA0~31 for RSA, and IDATA8~19 for ECC.

- 2. Set CONT[RUN], then wait until this bit is cleared.

- 3. Read OTEXT0~7(\*5) for the common-key ciphers, ODATA0~31 for RSA, and ODATA0~3 for ECC.

- (\*1) When selecting AES6, also set the round selection registers (KRSEL, DRSEL) as necessary.

- (\*2) Only for AES12 and AES13 that require initial values.

- (\*3) Only for AES8, AES9, and AES10 that use random numbers.

- (\*4) Set ITEXT0~3 for 64-bit block ciphers.

- (\*5) Read OTEXT0-3 for 64-bit block ciphers.

When AES6 is selected, the intermediate value either at the round designated in the round selection register or at fault is accessible on RDATA0~7. Likely, the intermediate key is accessible on RKEY0~7.

Settings can be changed as follows:

- To change the cryptographic core, perform the sequence from (a) through (h) again.

- To change the operating modes of the already selected cryptographic core, perform the sequence from (d) through (h) again.

- To change the key of the already selected cryptographic core, perform the sequence from (e) through (h) again.

- To change the initial value of the already selected cryptographic core, perform the sequence from (f) through (h) again.

- To change the random number of the already selected cryptographic core, perform the sequence from (g) through (h) again.

- AES5 (CTR mode + 4-stage pipeline implementation)

- (a)~(e) Same as the previous sequence.

- (f) Initial value (IV) setting

- 1. Set IV0~7.

- 2. Set 1 to the control register CONT[RUN], then wait until this bit is cleared.

- (g) Random number (seed) setting : No need to set.

- (h) Cryptographic operation : Repeat the following sequence.

- 1. Set ITEXT0~31.

- 2. Set 1 to the control register CONT[RUN], then wait until this bit is cleared.

- 3. Read OTEXT0~31.

To change the initial value, perform the sequence from (f) through (h) again.

| Туре           | Address   | Register name               | Mnemonic | R/W | Function/Description                                                                                                                                |

|----------------|-----------|-----------------------------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|                | 0000      | (Reserved)                  |          | —   |                                                                                                                                                     |

|                | 0002      | Control register            | CONT     | R/W | Starts operation(W)/Notifies completion(R).<br>Starts key generation(W) / Notifies<br>completion(R).<br>Controls resetting the cryptographic IP(W). |

|                | 0004      | IP selection register 0     | IPSEL0   | R/W | Designates the operating cryptographic IP.                                                                                                          |

|                | 0006      | IP selection<br>register 1  | IPSEL1   |     | Designates the operating cryptographic IP.                                                                                                          |

| System control | 0008      | Output selection register 0 | OUTSEL0  | R/W | Designates the data-exporting cryptographic IP.                                                                                                     |

| control        | 000A      | Output selection register 1 | OUTSEL1  | R/W | Designates the data-exporting cryptographic IP.                                                                                                     |

|                | 000C      | Mode register               | MODE     | R/W | Designates the operating modes, key length, and encryption/decryption.                                                                              |

|                | 000E      | Round selection register    | RSEL     | R/W | Designates the intermediate value keeping round.                                                                                                    |

|                | 0010      | Test register 1             | TEST1    | R/W | Custom core operation control 1                                                                                                                     |

|                | 0012      | Test register 2             | TEST2    | R/W | Custom core operation control 2                                                                                                                     |

|                | :<br>00FE | (Reserved)                  |          |     |                                                                                                                                                     |

Table 2.4Interface Registers (1/3)

| Type         Address         Register name         Mnemonic         R/W         Function/Description |                            |           |                                 |          |     |                                                   |  |  |

|------------------------------------------------------------------------------------------------------|----------------------------|-----------|---------------------------------|----------|-----|---------------------------------------------------|--|--|

|                                                                                                      | Туре                       | Address   | Register name                   | Mnemonic | K/W |                                                   |  |  |

|                                                                                                      |                            | 0100      | Key register 0                  | KEY0     | W   | Common-key algorithm's key (Top 16 bits)          |  |  |

|                                                                                                      |                            | 0102      | Key register 1                  | KEY1     | W   | Common-key algorithm's key (Next 16 bits to KEY0) |  |  |

|                                                                                                      | (→LSI)                     | :         | :                               | :        | :   | •                                                 |  |  |

|                                                                                                      |                            | 010E      | Key register 7                  | KEY7     | W   | Common-key algorithm's key<br>(Bottom 16 bits )   |  |  |

|                                                                                                      |                            | 0110      | IV register 0                   | IV0      | W   | Designates IV (Top 16 bits).                      |  |  |

|                                                                                                      | IV                         | 0112      | IV register 1                   | IV1      | W   | Designates IV (next 16 bits to IV0).              |  |  |

|                                                                                                      | (→LSI)                     | :         | :                               | :        | :   | •                                                 |  |  |

|                                                                                                      |                            | 011E      | IV register 7                   | IV7      | W   | Designates IV (Bottom 16 bits).                   |  |  |

|                                                                                                      |                            | 0120      | Input text register 0           | ITEXT0   | W   | Designates input text (Top 16 bits)               |  |  |

|                                                                                                      | Input text                 | 0122      | Input text register 1           | ITEXT1   | W   | Designates input text (Next 16 bits to ITEXT0)    |  |  |

|                                                                                                      | (→LSI)                     | :         | :                               | :        | :   | :                                                 |  |  |

|                                                                                                      |                            | 015E      | Input text register 31          | ITEXT31  | W   | Designates input text (Bottom 16 bits)            |  |  |

|                                                                                                      |                            | 0160      | Random number register<br>0     | RAND0    | W   | Designates random number (Top 16 bits)            |  |  |

| Comm                                                                                                 | Random<br>number<br>(→LSI) | 0162      | Random number register 1        | RAND1    | W   | Designates random number (Next 16 bits to RAND0)  |  |  |

| lon                                                                                                  |                            | :         | :                               | :        | :   | •                                                 |  |  |

| Common-key cryptography                                                                              |                            | 016E      | Random number register<br>7     | RAND7    | W   | Designates random number (Bottom 16 bits)         |  |  |

| ryptog                                                                                               | (Reserved)                 | :<br>017E | (Reserved)                      |          |     |                                                   |  |  |

| graj                                                                                                 |                            | 0180      | Output text register 0          | OTEXT0   | R   | Reads output text (Top 16 bits)                   |  |  |

| phy                                                                                                  | Output text                | 0182      | Output text register 1          | OTEXT1   | R   | Reads output text (Next 16 bits to OTEXT0)        |  |  |

|                                                                                                      | (←LSI)                     | :         | :                               | :        | :   | •                                                 |  |  |

|                                                                                                      |                            | 01BE      | Output text register 31         | OTEXT31  | R   | Reads output text (Bottom 16 bits)                |  |  |

|                                                                                                      |                            | 01C0      | Intermediate data<br>register 0 | RDATA0   | R   | Reads intermediate data (Top 16 bits)             |  |  |

|                                                                                                      | Intermediate<br>data       | 01C2      | Intermediate data register 1    | RDATA1   | R   | Reads intermediate data (Next 16 bits to RDATA0)  |  |  |

|                                                                                                      | (←LSI)                     | :         | :                               | :        | :   | :                                                 |  |  |

|                                                                                                      |                            | 01CE      | Intermediate data<br>register 7 | RDATA7   | R   | Reads intermediate data (Bottom 16 bits)          |  |  |

|                                                                                                      |                            | 01D0      | Intermediate key register<br>0  | RKEY0    | R   | Reads intermediate key (Top 16 bits)              |  |  |

|                                                                                                      | Intermediate<br>key        | 01D2      | Intermediate key register<br>1  | RKEY1    | R   | Reads intermediate key (Next 16<br>bits to RKEY0) |  |  |

|                                                                                                      | (←LSI)                     | :         | :                               | :        | :   | :                                                 |  |  |

|                                                                                                      |                            | 01DE      | Intermediate key register<br>7  | RKEY7    | R   | Reads intermediate key (Bottom 16 bits)           |  |  |

|                                                                                                      | (Reserved)                 | :<br>01FE | (Reserved)                      |          |     |                                                   |  |  |

Table 2.4Interface Registers (2/3)

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Tuble 2.4     Interface Registers (3/3)       Tuble 2.4     Interface Registers (3/3) |              |           |                         |          |    |                                                    |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------|-----------|-------------------------|----------|----|----------------------------------------------------|--|--|

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Туре                                                                                  |              | Address   | U U                     |          |    | *                                                  |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |              | 0200      | Exponent register 0     | EXP0     | W  |                                                    |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       | -            | 0202      | Exponent register 1     |          |    |                                                    |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |              | :         | •                       | :        | :  | :                                                  |  |  |

| $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                       | (* 151)      | 023E      | Exponent register 31    | EXP31    | W  | Sets exponent (Bottom 16 bits)                     |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |              | :         | •                       | :        | •• | :                                                  |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |              | 0300      | Modulus register 0      | MOD0     | W  | Sets modulus (Top 16 bits)                         |  |  |

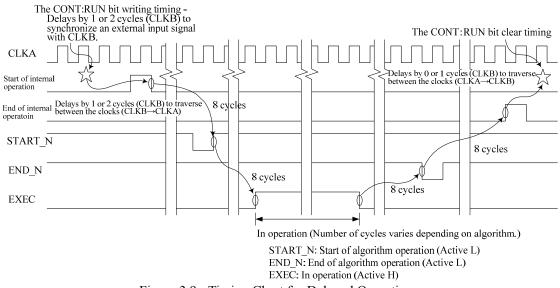

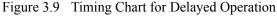

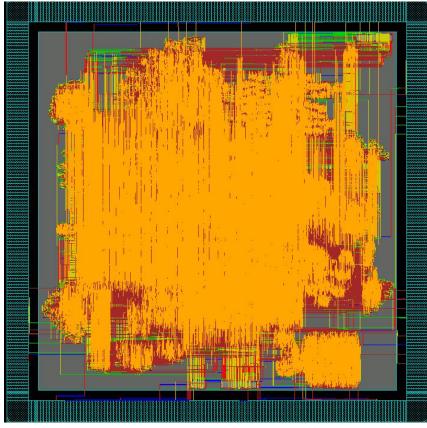

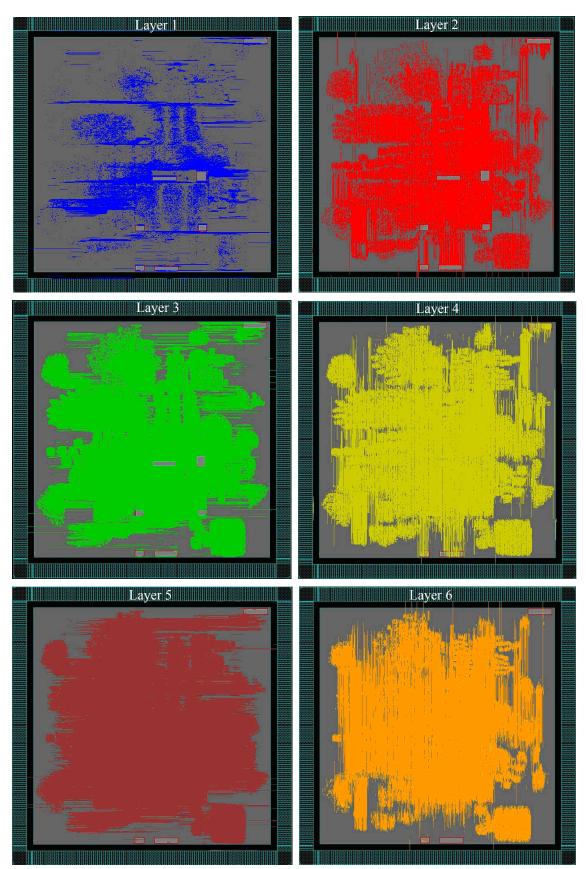

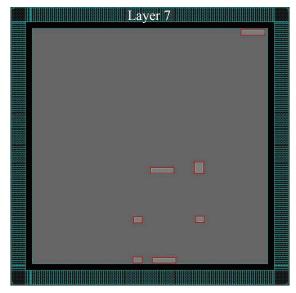

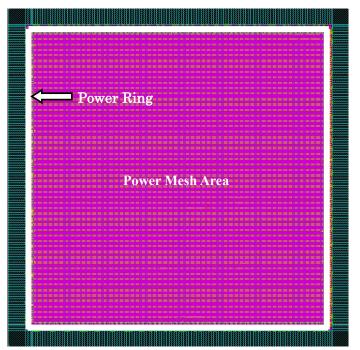

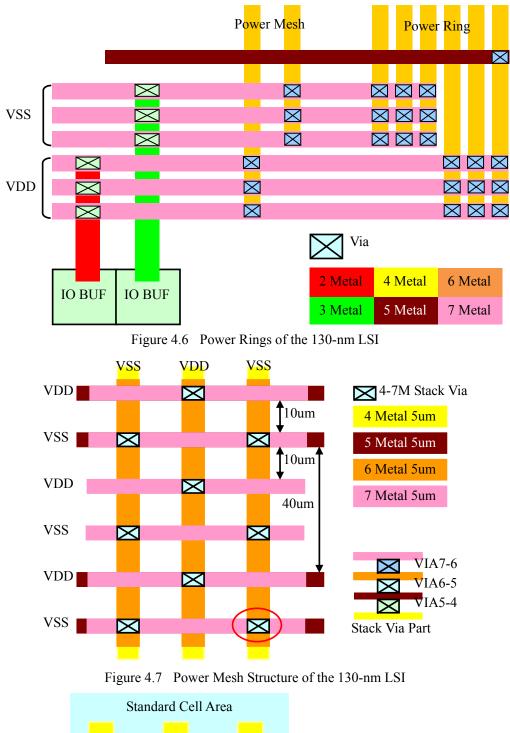

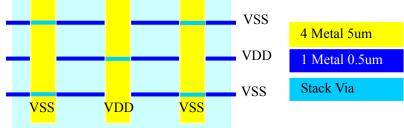

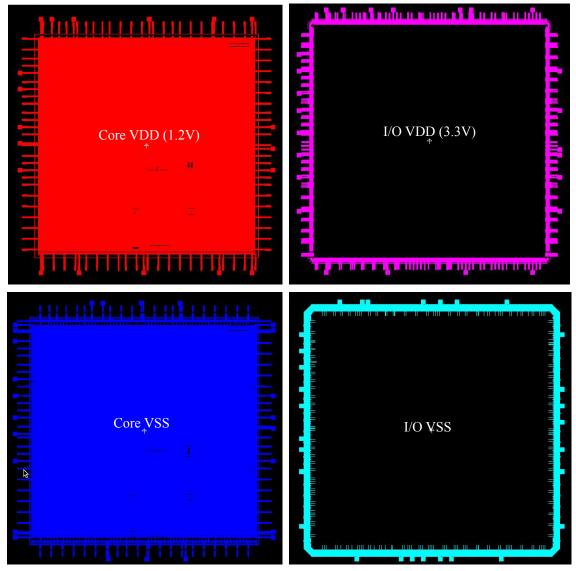

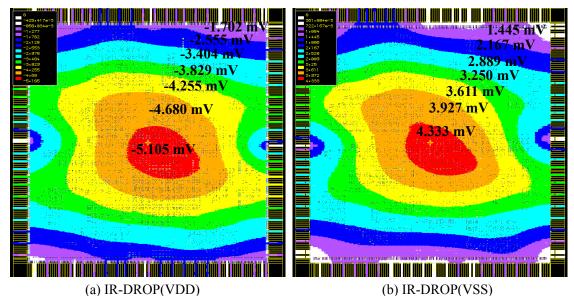

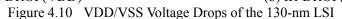

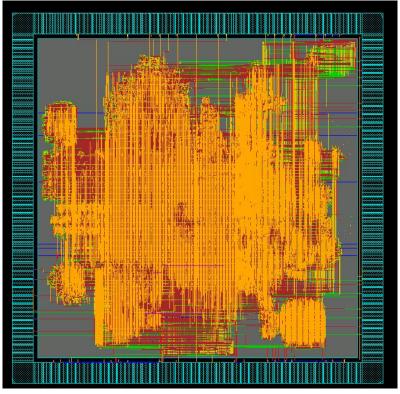

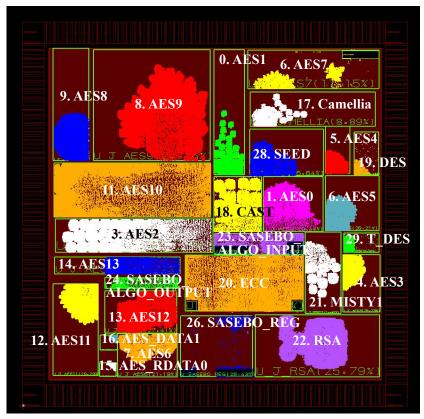

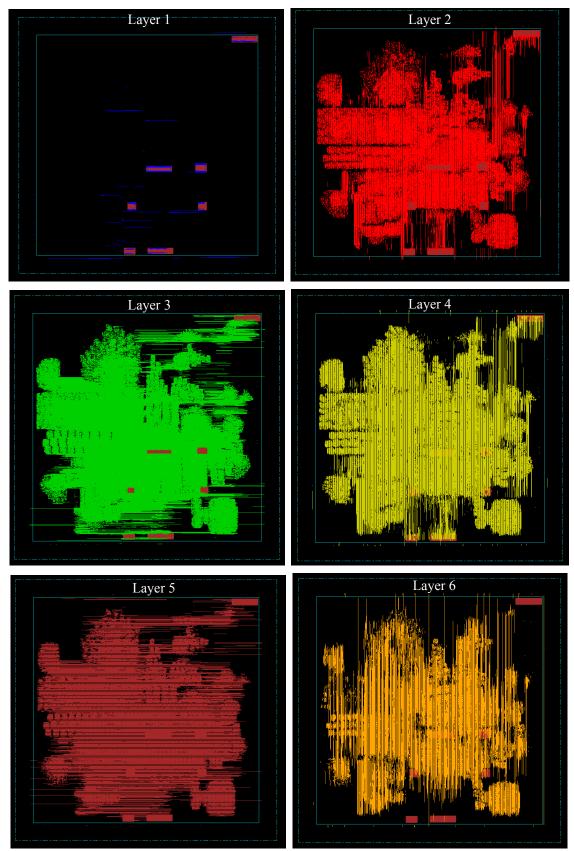

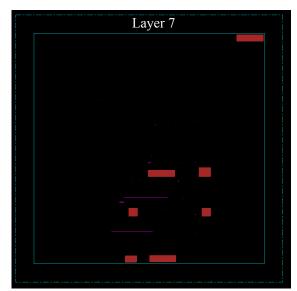

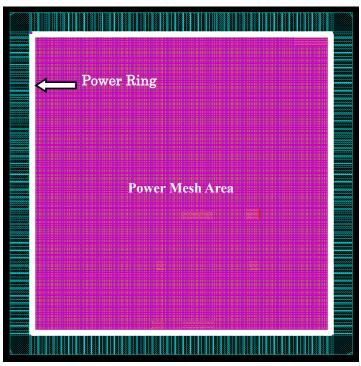

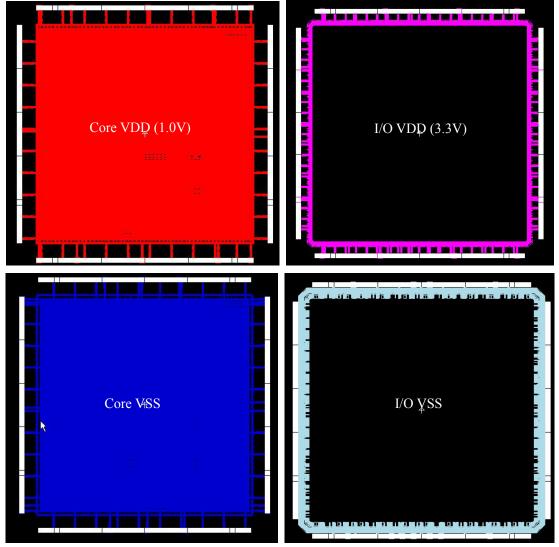

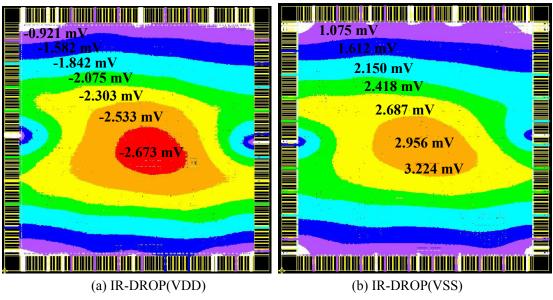

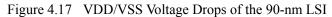

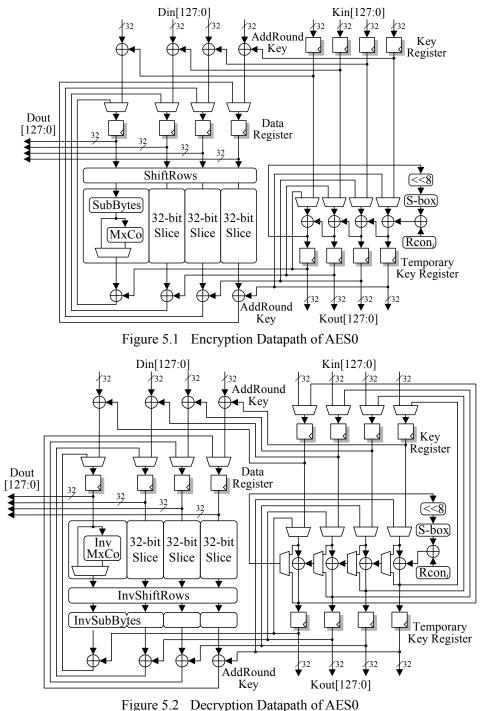

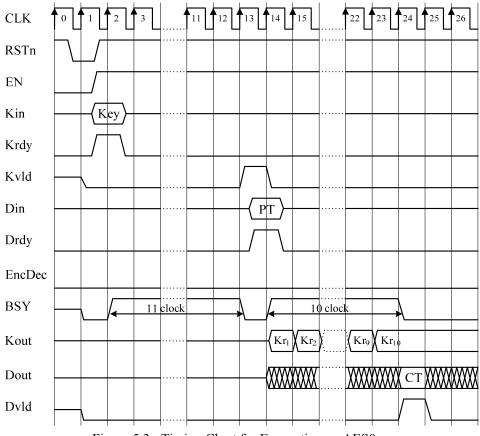

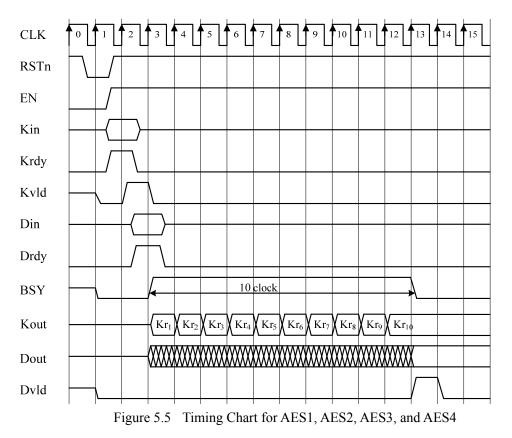

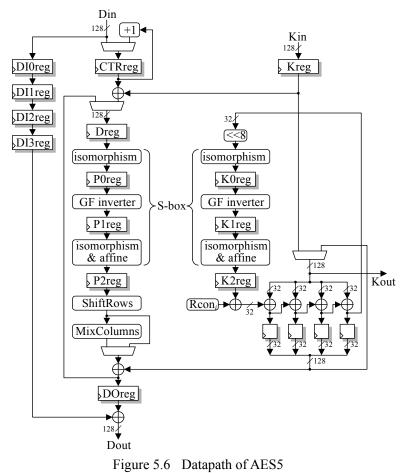

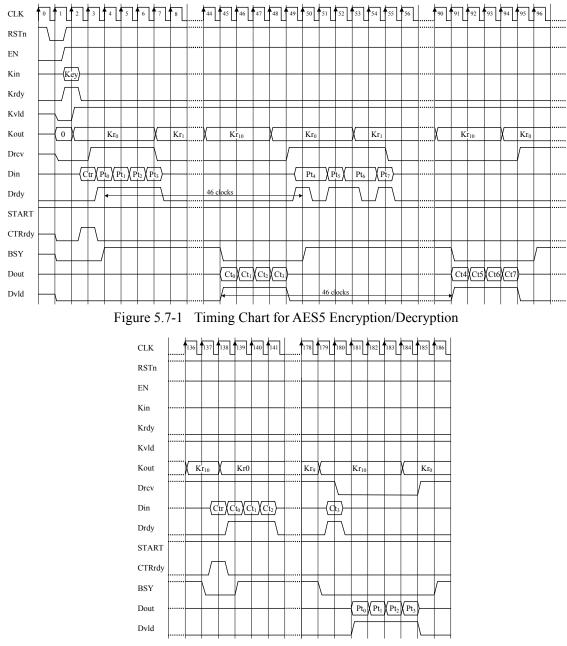

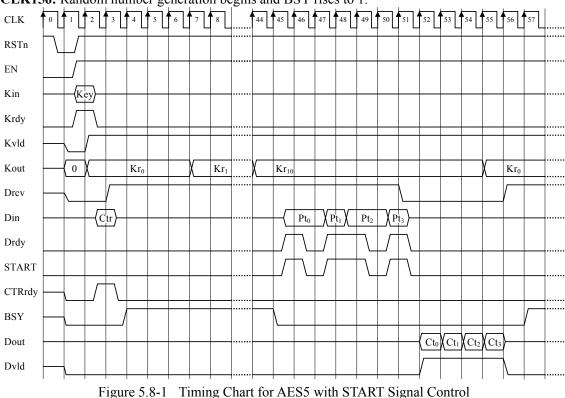

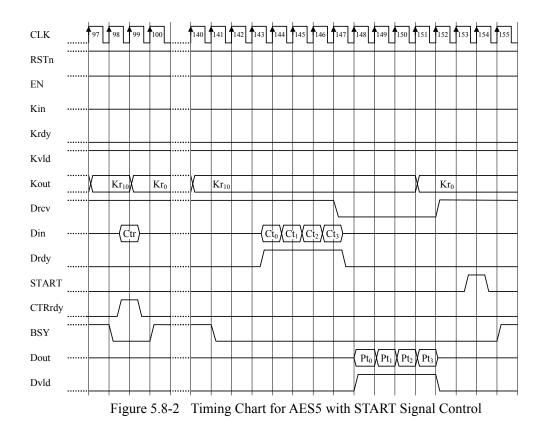

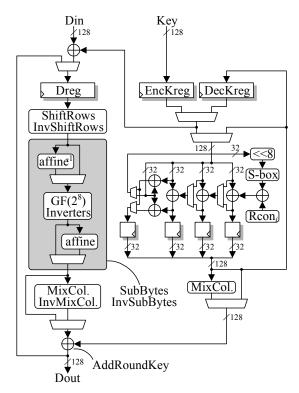

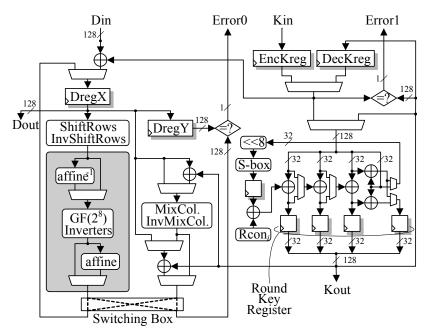

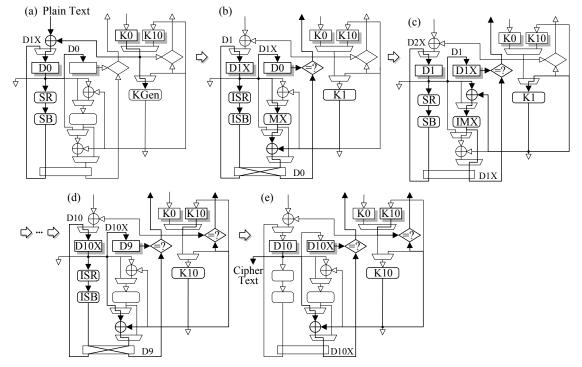

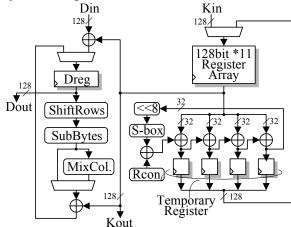

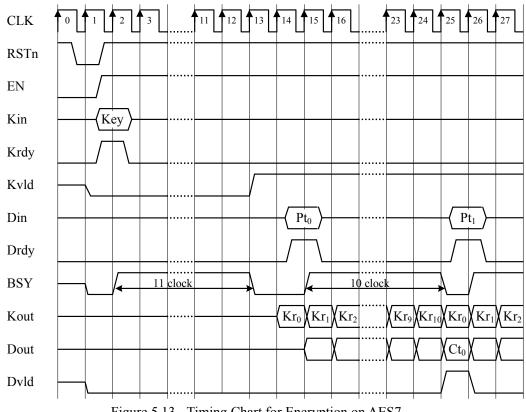

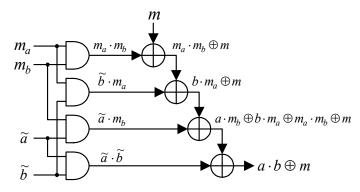

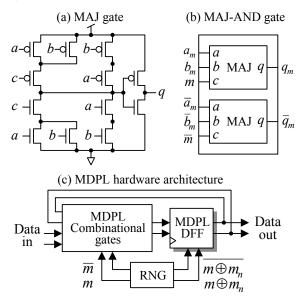

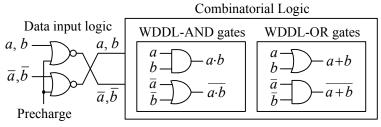

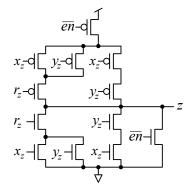

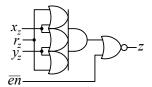

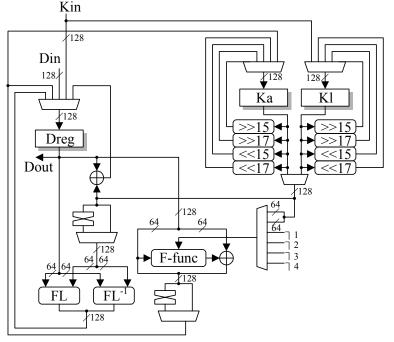

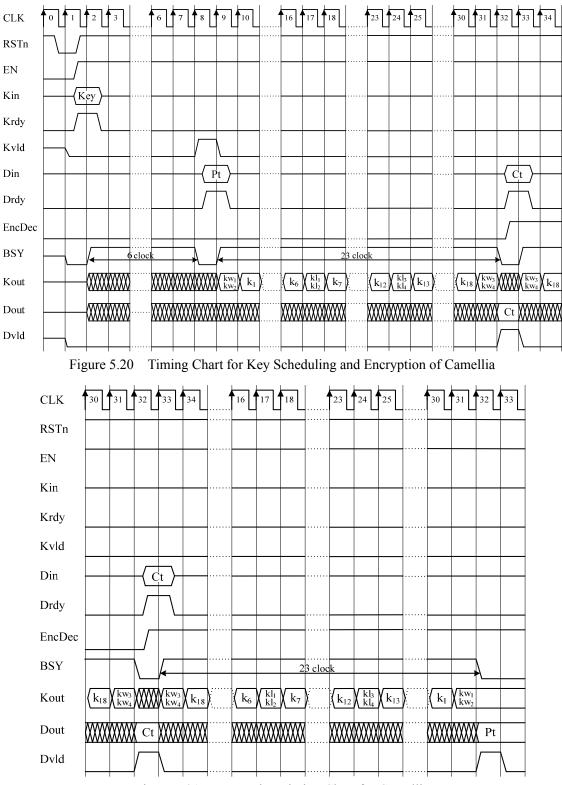

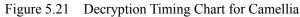

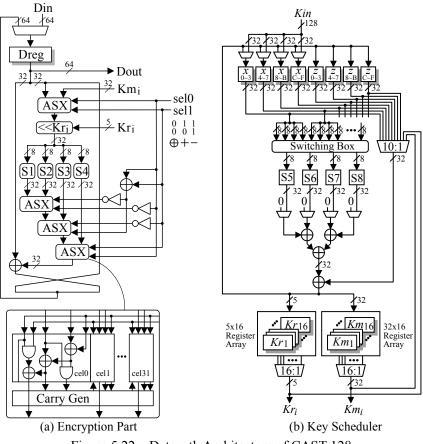

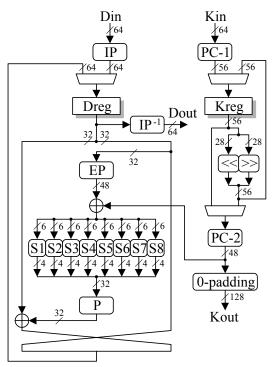

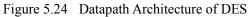

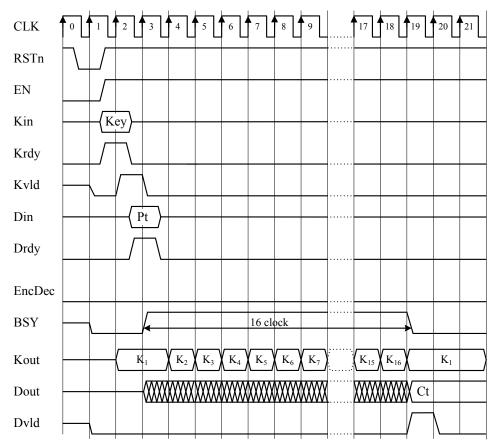

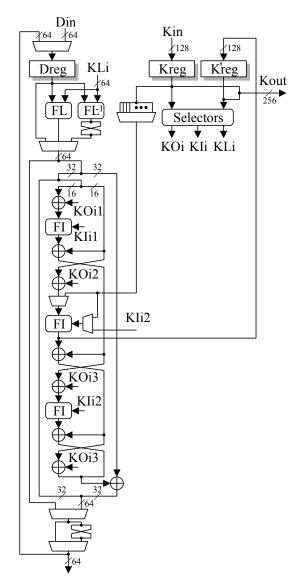

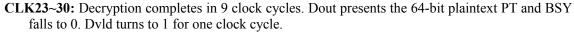

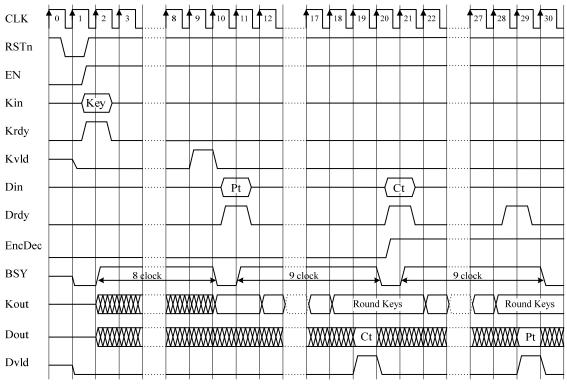

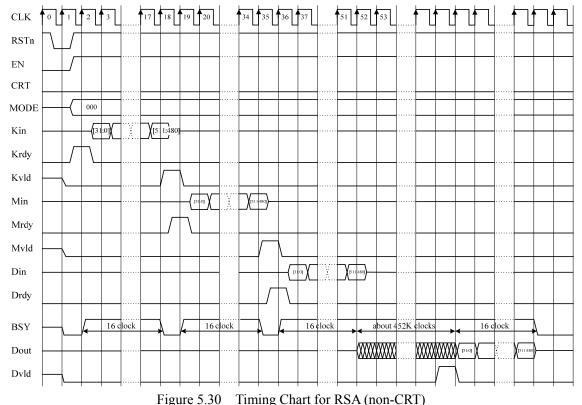

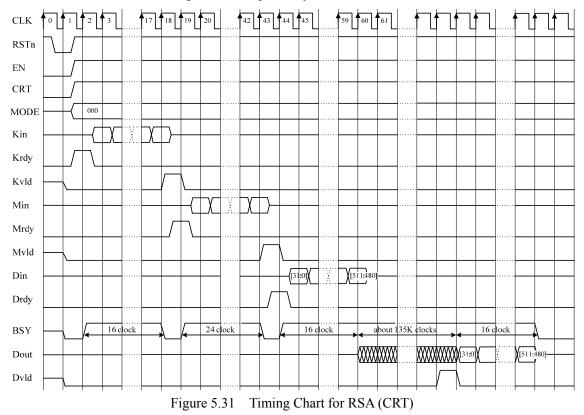

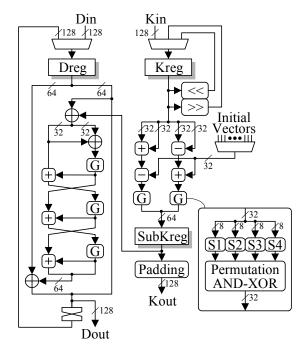

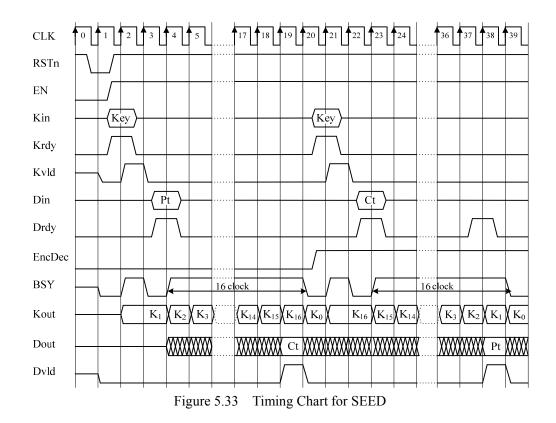

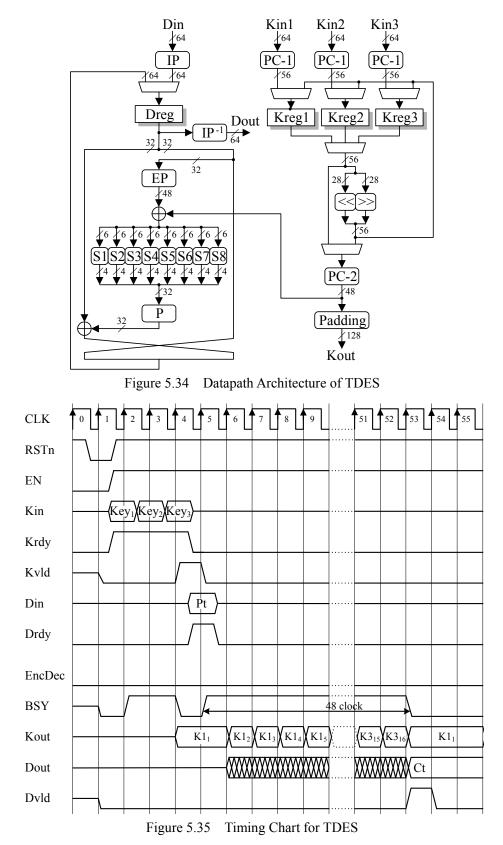

| $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                       |              | 0302      | Modulus register 1      | MOD1     | W  |                                                    |  |  |